9.1: DESCRIPCIÓN DEL CIRCUITO

- Page ID

- 84254

El propósito de esta sección es ilustrar con el ejemplo una manera en que el amplificador básico de dos etapas puede expandirse en un amplificador operacional completo y útil. Secciones posteriores de este capítulo analizan el circuito para determinar su rendimiento, mostrar cómo puede ser compensado para adaptar su función de transferencia de bucle abierto para su uso en aplicaciones específicas, e indican cómo las alternativas de diseño podrían afectar el rendimiento.

No se intenta justificar esta particular implementación del amplificador de dos etapas más que señalar que el circuito fue diseñado al menos en parte por su valor educativo. Una apreciación de las características sobresalientes de este circuito en particular conduce directamente a una mejor comprensión de otros amplificadores operativos, incluyendo una serie de diseños de circuitos integrados, que han evolucionado a partir de la topología básica. Las modificaciones incorporadas al diseño básico no son ciertamente las únicas posibles, ni todas son susceptibles de ser requeridas en una aplicación dada. El circuito sí ilustra cómo un diseñador podría resolver algunas de las compensaciones disponibles para él, y también proporciona un fondo para gran parte del material en secciones posteriores.

Visión general

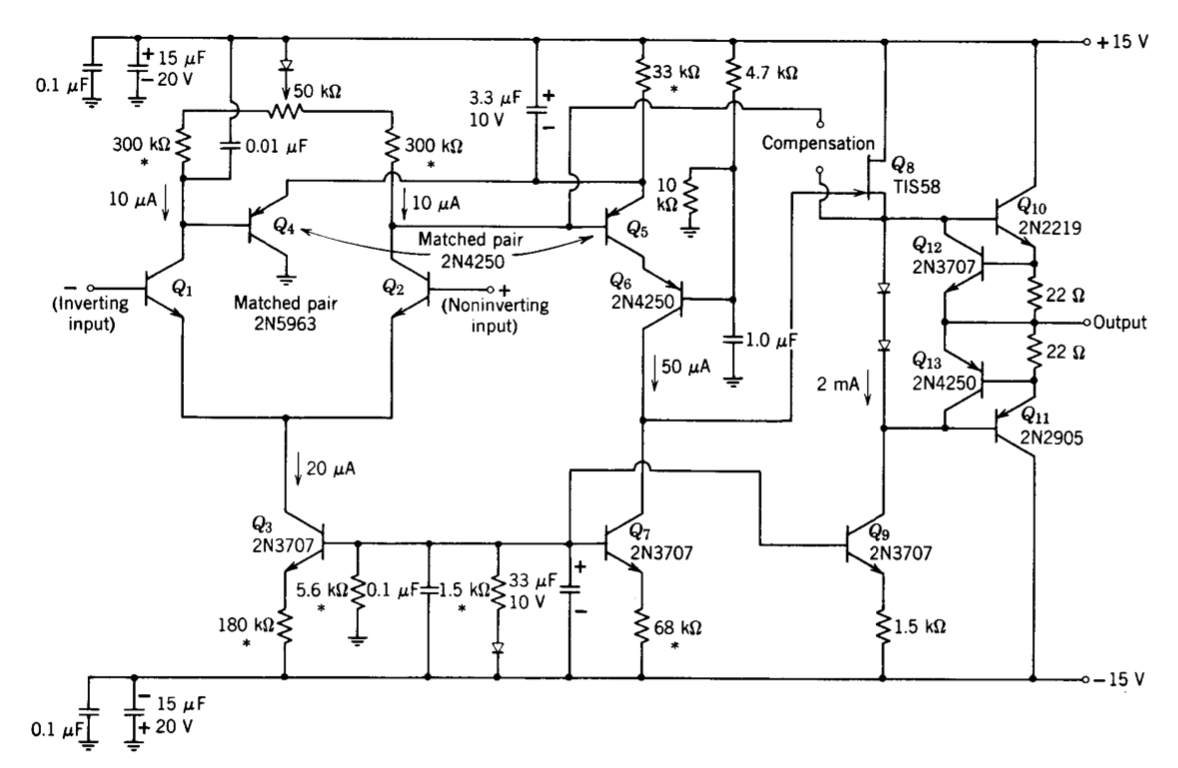

El circuito completo y los importantes niveles de quiescencia se muestran en la Figura 9.1. El circuito representa una modificación del amplificador básico que combina un amplificador diferencial que incorpora varias de las técnicas de minimización de deriva descritas en el Capítulo 7 con una etapa de alta ganancia que consiste en un amplificador cascode cargado con fuente de corriente. Un amplificador de búfer de ganancia de voltaje unitario aísla el nodo de alta resistencia en la salida del amplificador cascode y proporciona una capacidad de accionamiento de salida de alta corriente. El amplificador está diseñado para proporcionar una señal de salida\(\pm 10-\text{volt}\) máxima y operar desde\(\pm 15-\text{volt}\) fuentes estándar. Los voltajes de alimentación son ambos desviados con una combinación paralela de un condensador electrolítico y uno cerámico, ya que esta combinación es efectiva en un amplio rango de frecuencias.

Este circuito comparte una característica con una serie de otros diseños moderadamente involucrados, lo que a menudo es perturbador para los diseñadores de circuitos novatos ya que hay alguna dificultad para determinar qué transistores están realmente en la ruta de la señal. Es importante resolver esta incertidumbre antes de cualquier discusión detallada del circuito. Haciendo referencia a la Figura 9.1, vemos que los transistores\(Q_1\) y\(Q_2\) son la etapa de entrada de amplificador diferencial. Como veremos, la topología de la segunda etapa restringe la conexión del emisor del\(Q_4-Q_5\) par para que se ponga a tierra de manera incremental. Así\(Q_5\) y\(Q_6\) formar un amplificador cascode. Este cascode cargado con fuente de corriente proporciona la fracción más grande de la ganancia del amplificador, con análisis que se presentará indicando una ganancia de voltaje de 180,000 en esta porción del circuito.

El nodo de alta resistencia en la salida del amplificador cascode está aislado con FET conectado a la fuente de seguimiento\(Q_8\). El seguidor de fuente acciona los transistores\(Q_{10}\) y\(Q_{11}\), que están conectados como un seguidor de emisor complementario.

El amplificador se puede compensar conectando un trabajo neto apropiado entre los terminales indicados, formando así un bucle menor que incluye la etapa de alta ganancia. Los detalles de este proceso se dan en la Sección 9.2.3.

La discusión anterior muestra que la trayectoria de la señal incluye solo transistores\(Q_1, Q_2, Q_5, Q_6, Q_8, Q_{10}\), y\(Q_{11}\). Los transistores restantes se utilizan ya sea como fuentes de corriente (\(Q_3\),\(Q_7\), y\(Q_9\)), o para reducir la deriva de voltaje referida a la entrada mediante la formación de una segunda etapa diferencial en d-c (\(Q_4\)), o para limitar la corriente de salida (\(Q_{12}\)y\(Q_{13}\)).

Consideraciones detalladas

Una vez seleccionada la topología del circuito, una decisión sobre los niveles aproximados de polarización-corriente es un primer paso necesario en el proceso de diseño detallado. Los bajos niveles de corriente proporcionan un mejor rendimiento d-c ya que se reducen las corrientes de entrada y el autocalentamiento de la etapa de entrada. Sin embargo, la respuesta de frecuencia del amplificador se reduce por el funcionamiento a corrientes bajas. (Consulte la Sección 9.3.3 para obtener una descripción de las compensaciones entre potencia y velocidad).

Se seleccionó un nivel de corriente de colector de compromiso de\(10\ \mu A\), que puede proporcionar un excelente rendimiento d-c combinado con una respuesta de frecuencia de bucle cerrado de varios MHz, para los transistores de primera etapa. \(Q_3\)El transistor es una fuente de corriente que proporciona la corriente de\(20-\mu A\) reposo total de la primera etapa y asegura una alta relación de rechazo en modo común. Esta fuente de corriente comparte una red de polarización común con otras dos fuentes de corriente. La red de polarización incluye un diodo que proporciona compensación de temperatura aproximada para las fuentes de corriente, y también incluye derivación capacitiva a la fuente negativa. En este caso es preferible pasar por alto al suministro negativo en lugar de a tierra, ya que asegura que la salida de la fuente de corriente sea independiente de los transitorios de alta velocidad en la línea de suministro negativo.

La etapa de entrada diferencial es un par emparejado de transistores 2N5963. Los dispositivos se seleccionan para tener voltajes de base a emisor adaptados dentro de 3 mV a corrientes de colector iguales y, además, para tener ganancias de corriente coincidentes dentro del 10% al nivel de corriente de operación. Se montan en estrecha proximidad térmica para reducir los diferenciales de temperatura. Envolver el cable alrededor del par o montarlos en un bloque de aluminio perforado para aceptar los transistores mejora la unión térmica. El 2N5963 se selecciona porque es económico y proporciona una ganancia de corriente típica de 1100 a una corriente de colector de\(10 \mu A\). La corriente de polarización resultante requerida en cualquiera de las entradas es aproximadamente\(10\ nA\) sin ninguna forma de compensación de corriente. Técnicas de compensación como las descritas en la Sección 7.4.2 se pueden utilizar para reducir esta corriente de polarización a menos que en un\(1\ nA\) rango de\(50^{\circ} C\) temperatura.

Transistores\(Q_5\) y\(Q_6\) son los transistores de cascode-amplificador. Un transistor PNP adicional,\(Q_4\), se utiliza para mejorar el rendimiento d-c mediante la formación de un amplificador diferencial con transistor\(Q_5\). Si bien este transistor disminuye la deriva, no afecta el funcionamiento del\(Q_5-Q_6\) par de ninguna manera como se muestra en la siguiente discusión. Es evidente que a bajas frecuencias el punto de par emisor común\(Q_4-Q_5\) se pone a tierra incrementalmente ya que solo las señales diferenciales

se puede aplicar a este par por la etapa de entrada. El condensador (Como cuestión de interés práctico, eliminar este condensador solo tiene un efecto menor en el rendimiento general del amplificador, pero complica el análisis. Este es un ejemplo de un componente incluido principalmente con fines educativos.) incluido a través de la resistencia\(33-k\Omega\) emisor-circuito garantiza que el emisor de\(Q_5\) también permanece conectado a tierra incrementalmente a altas frecuencias. Dado que el transistor\(Q_4\) se incluye solo para mejorar el rendimiento d-c y no se requiere para ganancia a ninguna frecuencia, su circuito base puede ser desviado a frecuencias moderadas y altas. La derivación asegura que\(Q_1\) opera como una etapa de colector común en estas frecuencias. Se mencionó en el último capítulo que el funcionamiento en este modo es ventajoso ya que minimiza la capacitancia de entrada vista en la base de\(Q_1\) (la entrada inversora del amplificador completo), y así permite un mayor rango de redes de retroalimentación para ser utilizadas sin carga significativa de alta frecuencia.

El amplificador se equilibra cambiando los valores relativos de la resistencia de carga del colector en la primera etapa. Dado que los transistores de etapa de entrada están adaptados para un diferencial de voltaje máximo de base a emisor de 3 mV a corrientes de colector iguales, la relación de las corrientes de colector será como máximo\(e^{3mV(q/kT)} \simeq 1.12\) a tensiones iguales de base a emisor. Por lo tanto, el\(50-k\Omega\) potenciómetro que permite una relación colector-resistencia máxima de 1. 17:1 es adecuado para equilibrar incluso si existe algún desajuste de las corrientes de base de la segunda etapa. El diodo incluido en el circuito\(Q_1-Q_2\) colector proporciona un grado de compensación para los cambios de voltaje de base a emisor de los transistores\(Q_4-Q_5\) con temperatura para estabilizar su corriente de reposo.

Los transistores 2N4250 utilizados en la segunda etapa son uno de los tipos PNP de mayor ganancia disponibles, con una ganancia de corriente típica superior a 300 at\(50\ \mu A\) de corriente de colector. Esta ganancia permite un aumento de cinco a uno en el nivel operativo en reposo entre la primera y la segunda etapa (valioso ya que este aumento mejora el ancho de banda de los dispositivos de la segunda etapa) sin comprometer seriamente el rendimiento de deriva. También contribuye a una alta ganancia general del amplificador. Si bien no es necesario usar el mismo tipo de transistor para ambos miembros de un par de amplificadores cascode, el 2N4250 también se usa en la sección de base común del cascode (\(Q_6\)) ya que tiene alta\(r_{\mu}\), una condición necesaria para la ganancia de alto voltaje. El 2N3707 utilizado como carga de fuente de corriente para el cascode también se selecciona en parte debido a la alta\(r_{\mu}\).

Todas las resistencias críticas asociadas con las dos primeras etapas son tipos de película metálica de precisión. Estos son los preferidos ya que sus coeficientes de baja temperatura reducen la deriva de voltaje y debido a sus características de bajo ruido.

Se utiliza un transistor de efecto de campo para aislar el nodo de alta impedancia en la salida cascode. La resistencia de entrada prácticamente infinita del FET mejora la ganancia de voltaje. También se logra economía de componentes, ya que probablemente se requeriría una etapa adicional de ganancia de corriente para el aislamiento si se utilizaran transistores bipolares. Se utiliza una fuente de corriente para la polarización FET de modo que la corriente de polarización sea independiente del nivel de voltaje de salida. El nivel de reposo de esta etapa se elige para cumplir con los requisitos máximos de accionamiento para la siguiente etapa.

Se utiliza un par emisor-seguidor complementario (\(Q_{10}-Q_{11}\)) para proporcionar grandes corrientes de salida positivas o negativas con disipación de potencia mínima en reposo. En esta etapa se utilizan transistores de lata metálica en lugar de transistores con carcasa epoxi para aumentar la capacidad de manejo de energía. Los dos diodos incluidos en el circuito base del par emisor-seguidor reducen la distorsión de cruce, mientras que las\(22-\Omega\) resistencias eliminan la posibilidad de fuga térmica que acompaña a esta conexión.

Transistores\(Q_{12}\) y\(Q_{13}\) combinar con las\(22-\Omega\) resistencias para limitar la corriente de salida del amplificador a aproximadamente\(30\ mA\). Este circuito limitador, que es similar en funcionamiento al limitador de diodo descrito en relación con la Figura 8.27, se utiliza ya que es idéntico en forma a uno usado frecuentemente en diseños de circuitos integrados. Considera'el proceso limitante cuando el voltaje de salida del amplificador es negativo. Si la corriente de sumidero supera los 25 a\(30\ mA\), el transistor\(Q_{13}\) conduce, ya que su voltaje de base a emisor se aproxima a 600 mV. Esta conducción reduce la unidad base para\(Q_{11}\). La corriente que debe ser\(Q_{13}\) conducida para eliminar la impulsión base a\(Q_{11}\) es como mucho\(2\ mA\), el nivel de salida de la fuente de corriente\(Q_9\).

Cuando el voltaje de salida del amplificador es positivo, el transistor\(Q_{12}\) conduce para limitar la corriente de salida. Esta situación es potencialmente peligrosa, ya que es concebible que el transistor de accionamiento (\(Q_8\)) pueda ser destruido si ningún mecanismo limitara su corriente de drenaje. Sin embargo, la geometría del TIS58 es tal que su corriente de drenaje es del\(5\ mA\) orden en que la tensión puerta-fuente de este dispositivo alcanza el valor de conducción directa. Por lo tanto, mientras que el transistor\(Q_{12}\) puede conducir aproximadamente\(3\ mA\) en el límite de corriente de salida positiva, la destrucción de no\(Q_8\) es posible. Tenga en cuenta también que dado que la corriente máxima del colector de\(Q_6\) está limitada a valores modestos por la resistencia de\(33-k\Omega\) circuito emisor asociada con\(Q_4-Q_5\), la corriente máxima de\(Q_6\), no puede lesionar ningún dispositivo.

No se intenta controlar los voltajes internos del amplificador, como el potencial del emisor de\(Q_5\), durante la sobrecarga de corriente. La carga almacenada en el\(3.3-\mu F\) condensador retrasa la recuperación de la sobrecarga, pero dado que el límite de corriente no se anticipa durante el funcionamiento normal (la protección contra sobrecarga se incluye principalmente para protegernos de nuestros propios errores durante el breadboard del sistema), este retraso no es importante.