1.3: Tecnología de transistores

- Page ID

- 86047

Los transistores son dispositivos semiconductores con tres (y a veces más) terminales. El tercer terminal permite que la corriente de salida sea controlada por una señal de entrada relativamente pequeña y de baja potencia. En los amplificadores, los transistores se utilizan para lograr ganancia de corriente, ganancia de voltaje o ganancia de potencia. La mayoría de las veces la ganancia de potencia es el objetivo en el diseño de RF y microondas La mayoría de los transistores se fabrican usando silicio (Si) o semiconductores compuestos como galiumarsenida (GaAs), fosfuro de indio (InP) o nitruro de galio (GaN). La tendencia abrumadora es usar tecnología de silicio debido a la densidad de integración mucho mayor que es posible, con la tecnología de semiconductores compuestos utilizada solo cuando proporciona una ventaja única como alta potencia, rendimiento de ruido superior o alta eficiencia. El germanio se usa como dopante en el silicio y luego el silicio se conoce como germanio de silicio pero generalmente el germanio está en una proporción muy pequeña con respecto al silicio, por lo que SiGe como se describe aquí es silicio con un dopante. Con concentraciones comparables de silicio y germanio SiGe es un semiconductor compuesto y este se usa como semiconductor compuesto a veces.

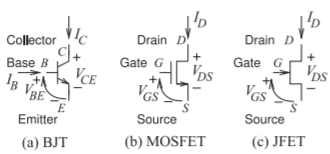

Existen tres tipos fundamentales de transistores de microondas [5, 6]: transistores de unión bipolar, (BJT); transistores de efecto de campo de unión, (JFET); y FET de puerta aislada, (IGFET), con el metal-óxido-semiconductor Los FET, (MOSFET), siendo el tipo más común de IGFET. Los esquemas y definiciones terminales de los tres tipos fundamentales de transistores se muestran en la Figura\(\PageIndex{1}\). Los tres tipos fundamentales de transistores se consideran en las siguientes subsecciones.

1.3.1 Fundamentos de BJT y HBT

Un transistor bipolar tiene tres regiones semiconductoras llamadas colector (C), base (B) y emisor (E), como se muestra en la sección transversal BJT de la Figura\(\PageIndex{2}\) (a). Un NPN BJT tiene un semiconductor tipo n en el emisor y el colector, y el semiconductor tipo p forma la base. En este transistor, el sentido positivo del flujo de corriente es desde el colector a través de la base hasta el emisor (ver Figura\(\PageIndex{2}\) (a)) y los portadores dominantes en la región base tipo p son electrones, por lo que esto se denomina dispositivo portador minoritario. La corriente del colector depende del número de portadoras inyectadas en la región base desde el terminal base. En un pnp BJT el colector, la base y el emisor son de tipo p, tipo n y tipo p, respectivamente, y la mayoría de las portadoras en la base son agujeros. El flujo de corriente es entonces desde el emisor a través de la base hasta el colector. Si la región base es delgada y el emisor está dopado a una concentración mayor que la base, entonces la corriente del colector,\(I_{C}\), es mucho mayor que\(I_{B}\), con\(I_{C} = \beta_{F}I_{B}\), donde\(\beta_{F}\) se denomina ganancia de corriente directa y comúnmente tiene un valor de varios cientos. La clave para un alto rendimiento es una región base delgada.

Cuando se realiza en silicio, un transistor bipolar se llama transistor de unión bipolar, (BJT); y en la tecnología de semiconductores compuestos es un transistor bipolar de heteroestructura, (HBT). En un transistor BJT de germanio de silicio (SiGe), el germanio se usa normalmente para aumentar la movilidad de agujeros y electrones y el dispositivo no se considera como un transistor semiconductor compuesto.

El funcionamiento fundamental de un transistor BJT fue descrito por Gummel y Poon [7] utilizando ecuaciones que ahora se implementan en simuladores de circuito y se conocen como el modelo Gummel—Poon. El esquema del circuito del modelo Gummel-Poon se muestra en la Figura\(\PageIndex{2}\) (c). Es la base para más

Figura\(\PageIndex{1}\): Esquemas de transistores: (a) transistor bipolar pnp con B para el terminal base, C para el terminal colector y E para el terminal emisor; (b) MOSFET de tipo n (NMO); y (c) JFET de tipo n (NJFET) con G para el terminal de puerta, D para el terminal de drenaje y S para el terminal fuente. El símbolo esquemático para un BJT se usa para HBT; y el símbolo esquemático para un JFET se usa para MESFET, HEMTS y PHEMT.

Figura\(\PageIndex{2}\): Detalles de BJT.

sofisticados modelos BJT y HBT que capturan efectos parasitarios y otros efectos de segundo orden. Tanto los portadores de carga de agujero como de electrones están involucrados en la conducción de corriente, de ahí el término bipolar. El modelo Gummel—Poon se describe en la Sección 1.A.3 y la operación fundamental se describe en las Ecuaciones (1.A.52) — (1.A.62). Resumiendo, la corriente base-emisor es

\[\label{eq:1}I_{BE}=I_{BF}/\beta_{F}+I_{LE} \]

y la corriente de colector base es

\[\label{eq:2}I_{BC}=I_{BR}/\beta_{R}+I_{LC} \]

donde\(\beta_{R}\) está la ganancia de corriente inversa. La corriente colector-emisor es

\[\label{eq:3}I_{CE}=I_{BF}-I_{BR}/K_{QB} \]

La corriente de difusión directa es

\[\label{eq:4}I_{BF}=I_{S}\left(\text{e}^{V_{BE}/(N_{F}V_{TH})}-1\right) \]

la corriente emisor-base no ideal es

\[\label{eq:5}I_{LE}=I_{SE}\left(\text{e}^{V_{BE}/(N_{E}V_{TH})}-1\right) \]

la corriente de difusión inversa es

\[\label{eq:6}I_{BR}=I_{S}\left(\text{e}^{V_{BC}/(N_{R}V_{TH})}-1\right) \]

la corriente de colector base no ideal es

\[\label{eq:7}I_{LC}=I_{SC}\left(\text{e}^{V_{BC}/(N_{C}V_{TH})}-1\right) \]

y el factor de carga base es

\[\label{eq:8}K_{QB}=\frac{1}{2}\left[1-\frac{V_{BC}}{V_{AF}}-\frac{V_{BE}}{V_{AB}}\right]^{-1}\left[1+\sqrt{1+4\left(\frac{I_{BF}}{I_{KF}}+\frac{I_{BR}}{I_{KR}}\right)}\right] \]

Por lo tanto, la corriente conductora que fluye hacia la base es

\[\label{eq:9} I_{B}=I_{BE}+I_{BC} \]

la corriente conductora que fluye hacia el colector es

\[\label{eq:10}I_{C}=I_{CE}-I_{BC} \]

y la corriente conductora que fluye hacia el emisor es

\[\label{eq:11}I_{E}=I_{BE}+I_{CE} \]

La ganancia de corriente directa\(\beta_{F}\),, es mucho mayor que la ganancia de corriente inversa\(\beta_{R}\), y las corrientes de base-emisor y colector de base no ideales son pequeñas. Ecuaciones\(\eqref{eq:1}\): luego se\(\eqref{eq:11}\) pueden reducir para que la corriente base sea aproximadamente

\[\label{eq:12}I_{B}=\frac{I_{S}}{\beta_{F}}\left(\text{e}^{V_{BE}/(N_{F}V_{TH})}-1\right) \]

la corriente conductora que fluye hacia el colector es

\[\label{eq:13}I_{C}=\beta_{F}I_{B} \]

y la corriente conductora que fluye hacia el emisor es

\[\label{eq:14}I_{E}=I_{B}+I_{C} \]

A partir de Ecuaciones\(\eqref{eq:12}\) y\(\eqref{eq:13}\) se ve que el funcionamiento fundamental de un BJT es como fuente de corriente controlada por voltaje. Esto conduce al modelo de circuito de señal pequeña de un BJT, polarizado en su modo fundamental de operación, mostrado en la Figura\(\PageIndex{2}\) (b).

Los símbolos esquemáticos utilizados para los BJT se muestran en la Tabla\(\PageIndex{1}\) con la flecha apuntando al semiconductor de tipo n. El símbolo BJT es también el símbolo de un HBT.

1.3.2 Fundamentos MOSFET

Existen varios tipos de FET, siendo el MOSFET el más común. Con todos los FET hay un canal entre dos terminales, la fuente y el drenaje, y un campo aplicado producido por una tensión en un tercer terminal, la puerta, controla la sección transversal del canal y el número de portadoras en el canal. De ahí que el voltaje de la puerta controle el flujo de corriente entre el drenaje y la fuente. Con algunos FET, el canal no existe hasta que se aplica un campo de puerta y extrae a los transportistas del bulto al canal, y esto

| Transistor | Símbolo IEEE | Símbolo de uso común |

|---|---|---|

| BJT, pnp |  |

|

| BJT, npn |  |

|

Tabla\(\PageIndex{1}\): Símbolos esquemáticos estándar IEEE para transistores de unión bipolar (BJT y HBT) [8] y símbolos de uso común en diseños [9]. Las letras indican terminales:\(\mathsf{B}\) (base),\(\mathsf{C}\) (colector),\(\mathsf{E}\) (emisor). Estos símbolos se utilizan para BJT de silicio y HBTs semiconductores compuestos.

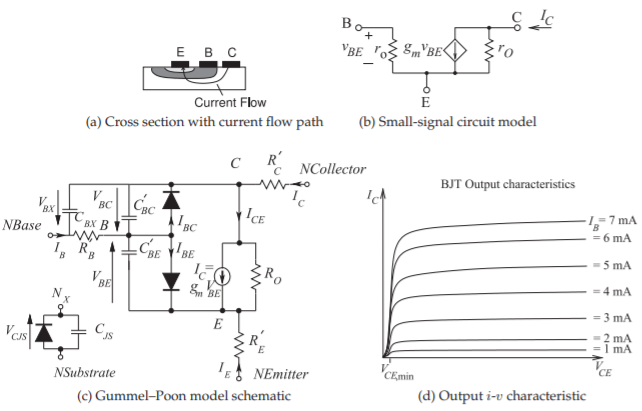

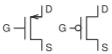

Figura\(\PageIndex{3}\): Características de corriente-voltaje de MOSFET de modo de agotamiento y mejora.

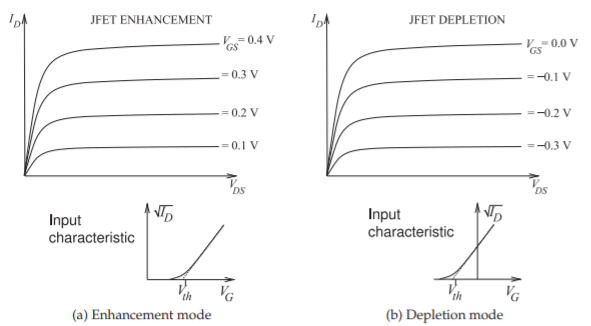

se llama FET de modo de mejora. Las características de entrada y salida del FET en modo de mejora se muestran en la Figura\(\PageIndex{3}\) (a). Con algunos MOSFET con un perfil de dopaje particular, los portadores están en el canal incluso sin un campo aplicado y un voltaje de puerta mejora la sección transversal del canal o lo cierra. La mayoría de las veces, el voltaje de la puerta se usa para reducir la conducción de corriente, y este tipo de FET se llama FET de modo de agotamiento. Las características de entrada y salida del FET en modo de agotamiento se muestran en la Figura\(\PageIndex{3}\) (b). El MOSFET de modo de mejora es mucho más común que el modo de agotamiento.

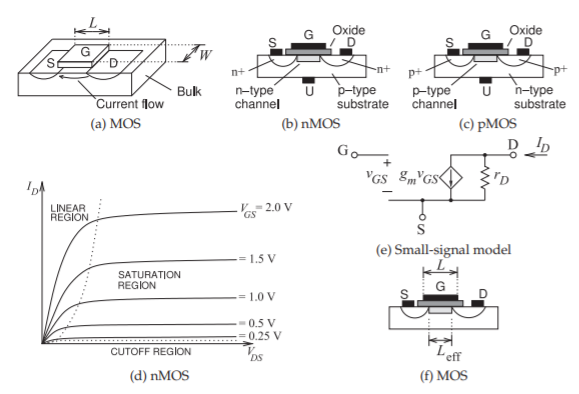

El MOSFET de mejora es un dispositivo relativamente simple de fabricar y es el más pequeño de los transistores semiconductores. Es la tecnología preferida para la integración de alta densidad. La vista tridimensional y las secciones transversales de un MOSFET se muestran en la Figura\(\PageIndex{4}\) (a—c). La sección transversal de un transistor NMO se muestra en la Figura\(\PageIndex{4}\) (b) donde hay un sustrato tipo p y se crea un canal tipo n cuando hay suficiente voltaje en la puerta. Además de la conexión de fuente y drenaje, hay una cuarta terminal llamada a la conexión del cuerpo denotada como\(\mathsf{U}\) en la Figura\(\PageIndex{4}\) (b) pero también\(\mathsf{B}\) se usa y esto se puede confundir con la base de un transistor BJT. El cuerpo es típicamente

Figura\(\PageIndex{4}\): Detalles MOSFET: (a) vista tridimensional de un MOSFET; (b) sección transversal de un transistor NMO con contactos metálicos o polisilicio indicados por los bloques negros; (c) la sección transversal correspondiente de un transistor PMO; (d) características de corriente-voltaje de un modo de mejora MOSFET; (e) modelo de circuito de funcionamiento fundamental; y (f) sección transversal que muestra la longitud efectiva de la puerta,\(L_{\text{EFF}}\). La región lineal a veces (pero con menos frecuencia) se llama región triodo debido a la similitud con las características del dispositivo de tubo de vacío triodo. De manera similar, la región de saturación a veces se llama región pentodo.

conectado a la tensión más negativa en el circuito para que la interfaz de sustrato a canal sea un diodo de polarización inversa. Una situación similar ocurre con el transistor PMO con la sección transversal de la Figura\(\PageIndex{4}\) (c). Ahora hay un canal tipo p y un sustrato tipo n de manera que el cuerpo (\(\mathsf{U}\)) normalmente debe estar conectado a la tensión más positiva en el circuito para asegurar una unión polarizada inversa entre el sustrato y el canal.

Un MOSFET tiene conexiones de metal o polisilicio (un conductor razonable [5, 6, 10]) en el drenaje (\(\mathsf{D}\)), la fuente (\(\mathsf{S}\)) y la puerta (\(\mathsf{G}\)). El MOSFET casi siempre es silicio, pero posiblemente (¡GaN! MOSFET [11, 12]. Las conexiones de fuente y drenaje son regiones semiconductoras altamente dopadas (n+ para NMO y p+ para PMO) que proporcionan un buen contacto óhmico en lugar de formar una barrera Schottky. \(^{1}\)La puerta no está en contacto directo con el semiconductor, sino separada por una fina capa de óxido. Sin voltaje aplicado en la puerta, no hay portadores debajo del óxido de la puerta que puedan conducir corriente entre la fuente y el drenaje. Es necesario un voltaje de puerta para atraer portadores a la región del canal, formando un canal conductor. Es decir, un voltaje aplicado a la puerta crea un campo eléctrico que induce electrones (los n portadores para un NMOSFET) para formar un canal conductor inmediatamente debajo del óxido. \(^{2}\)Este proceso se llama inversión. La longitud del canal se denota\(L_{\text{eff}}\) (la longitud efectiva de la puerta), que es menor que la longitud real de la puerta\(L\) ya que las regiones de fuente y drenaje altamente dopadas deben extenderse debajo de la puerta para asegurar un buen contacto con el canal inducido. Esto se indica en la Figura\(\PageIndex{4}\) (e). El número de portadores en el canal está controlado por la tensión de la puerta. Se obtiene una mayor frecuencia de operación al reducir\(L_{\text{eff}}\).

Tres regiones distintas de operación, identificadas en la Figura\(\PageIndex{4}\) (d), son reconocidas para un MOSFET. En la región lineal la corriente drenaje-fuente,\(I_{DS}\), continúa aumentando a medida que aumenta el voltaje drenaje-fuente\(V_{DS}\),,. \(I_{DS}\)depende tanto del voltaje drenaje-fuente como de la puerta-fuente,\(V_{DS}\) y, por lo tanto\(V_{GS}\), la región lineal a veces se explota en mezcladores. En la región de saturación,\(I_{DS}\) es casi independiente\(V_{DS}\) y casi exclusivamente controlada por\(V_{GS}\). Los amplificadores MOSFET operan en la región de saturación. La región de corte es cuando hay una corriente de drenaje insignificante, y un FET es particularmente efectivo para apagar la conducción y, por lo tanto, hace un buen interruptor controlado por voltaje.

En el diseño inicial se debe entender intuitivamente el modo de operación fundamental y se necesitan modelos y ecuaciones simples. En contraste, un simulador de circuito requiere un modelo detallado que capture efectos físicos sutiles. Un modelo de un MOSFET que puede ser utilizado en un simulador de circuito se presenta en la Sección 1.A.1. El modelo presentado se conoce como el modelo MOSFET de Nivel 3 y captura el funcionamiento fundamental de los MOSFET así como los efectos parasitarios capacitivos. Los modelos se desarrollan utilizando conocimientos físicos sobre el funcionamiento de los semiconductores. Todos los modelos de dispositivos semiconductores, no solo MOSFET, requieren un ajuste extenso a los datos medidos y tienen una precisión limitada. En consecuencia, el diseño, la fabricación y el ciclo de prueba son de vital importancia para realizar circuitos de transistores.

En la región de saturación (ver Figura\(\PageIndex{4}\) (d)) la operación fundamental de un MOSFET se describe mediante la Ecuación (1.A.27), la cual se repite aquí:

\[\label{eq:15}I_{DS}=\frac{W_{\text{eff}}}{L_{\text{eff}}}\mu_{\text{eff}}C_{ox}\left[(V_{GS}-V_{th})-1+\frac{F_{B}}{2}V_{d\text{sat}}\right]V_{d\text{sat}} \]

Aquí\(C_{ox}\) está la capacitancia del óxido de la puerta,\(W_{\text{eff}}\) es el ancho efectivo de la puerta, que es el ancho de la puerta\(W\) modificado por la franja y efectos relacionados,\(V_{th}\) es el voltaje umbral, y\(\mu_{\text{eff}}\) es la movilidad efectiva\(^{3}\) de los portadores en el canal ( electrones para un NMOSFET y agujeros para un pMOSFET). \(V_{d\text{sat}}\)es el voltaje de saturación de drenaje y es el voltaje de la fuente de drenaje en el que el dispositivo ingresa a la región de saturación desde la región lineal. \(F_{B}\)se debe a la carga en el semiconductor masivo (debajo del canal) en el que termina el campo eléctrico inducido por puerta. \(L_{\text{eff}}\)es la longitud efectiva de la puerta y esta es modulada por la tensión drenaje-fuente de manera que [5, 6, 10]

\[\label{eq:16}L_{\text{eff}}=\frac{L}{1+\lambda V_{DS}} \]

Contabilizando la modulación de la longitud del canal, descrita por la ecuación\(\eqref{eq:16}\), y simplificando [5, 6, 10], la ecuación\(\eqref{eq:15}\) se convierte en

\[\label{eq:17}I_{DS}=\frac{W}{L}\frac{\mu_{\text{eff}}C_{ox}}{2}(V_{GS}-V_{th})^{2}(1+\lambda V_{DS}) \]

Esta ecuación encarna la operación fundamental necesaria en el desarrollo de diseños iniciales. La clave es que el MOSFET pueda modelarse (al menos en la región de saturación) como una fuente de corriente controlada por voltaje como se muestra en el modelo de la Figura\(\PageIndex{4}\) (e). La transconductancia,\(g_{m}\) (en saturación), se obtiene diferenciando la Ecuación\(\eqref{eq:17}\) para que (ignorando la modulación de longitud de canal)

\[\label{eq:18}g_{m}=\frac{\partial I_{DS}}{\partial V_{GS}}=\frac{W}{L}\mu_{\text{eff}}C_{ox}(V_{GS}-V_{th}) \]

Esto también se puede escribir como

\[\label{eq:19}g_{m}=\sqrt{\frac{W}{L}2\mu_{\text{eff}}C_{ox}I_{DS}} \]

Generalmente la longitud de la puerta\(L\) se fija al mínimo soportado por un proceso en particular, ya que esto proporciona la mayor frecuencia de operación. Sin embargo, ambos\(L\) y se\(W\) pueden seleccionar para controlar la corriente,\(I_{DS}\). Por ejemplo, si\(V_{GS}\) es fijo, entonces el MOSFET actúa como fuente de corriente, con el valor de la corriente ajustado en diseño por ajuste\(L\) y\(W\) siempre que haya suficiente\(V_{DS}\).

Las características de corriente-voltaje mostradas en la Figura\(\PageIndex{4}\) (d) son las de un MOSFET de modo de mejora, que requiere el procesamiento más simple. La aplicación de un voltaje puerta-fuente mejora el canal y aumenta\(I_{DS}\). Con procesamiento adicional [5, 6, 10, 13] puede fabricarse un MOSFET de modo de agotamiento para que el canal exista incluso sin un voltaje de puerta aplicado. Las mismas ecuaciones se utilizan para describir la operación con el voltaje umbral cambiado. \(I_{DS}\)aumenta a medida que aumenta el voltaje puerta-fuente y se reduce a medida que el voltaje de puerta se vuelve negativo. El contraste entre MOSFET en modo de mejora y modo de agotamiento se ilustra en la Figura\(\PageIndex{3}\).

El voltaje del semiconductor masivo afecta el funcionamiento de un MOSFET y es un cuarto terminal que controla la conducción drenaje-fuente, pero tiene un efecto mucho menor que el de la puerta. La mayoría de las veces, el volumen se conecta eléctricamente al voltaje más negativo en un circuito para un NMOSFET y al voltaje más positivo para un PMOSFET. Los símbolos esquemáticos estándar de los MOSFET se muestran en la Tabla\(\PageIndex{2}\).

1.3.3 Fundamentos de MESFET, HEMT y JFET

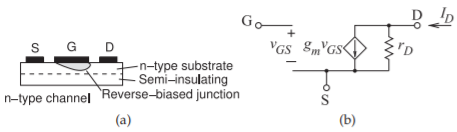

Los MESFETand HEMT son tipos de JFET fabricados con semiconductores compuestos, con JFET más comúnmente refiriéndose solo a dispositivos de silicio. La sección transversal de un JFET se muestra en la Figura\(\PageIndex{5}\) (a), donde la profundidad (sección transversal) del canal conductor se varía por el grosor de la región de agotamiento de una unión con polarización inversa. Con el JFET de silicio, el voltaje aplicado al terminal de puerta cambia la cantidad de polarización inversa y, por lo tanto, el grosor de la región de agotamiento. El aumento de la polarización inversa reduce la sección transversal del canal de transporte de corriente. Así, un JFET parece una conductancia variable. El campo de control del FET se crea en la unión pn con polarización inversa en

| Transistor | Símbolo IEEE | Símbolo de uso común (3 terminales) | Símbolo de uso común (4 terminales) |

|---|---|---|---|

| FET, ONM, agotamiento |  |

|

|

| FET, PMO, agotamiento |  |

|

|

| FET, NMO, mejora |  |

|

|

| FET, PMO, mejora |  |

|

|

Tabla\(\PageIndex{2}\): Símbolos esquemáticos estándar IEEE para transistores MOSFET [8] y símbolos más utilizados en esquemas [9]. Los símbolos MOSFET son para transistores de modo de mejora y agotamiento. Las letras indican terminales:\(\mathsf{G}\) (puerta),\(\mathsf{D}\) (drenaje),\(\mathsf{S}\) (fuente),\(\mathsf{U}\) (bulto). El símbolo NMOSFET de tres terminales se usa con mayor frecuencia cuando el bulk está conectado a la conexión más negativa en el circuito, y el símbolo PMOSFET de tres terminales se usa cuando el bulk está vinculado a\(V_{DD}\) (la conexión más positiva).

Figura\(\PageIndex{5}\): Detalles de JFET: (a) sección transversal; y (b) modelo de circuito de funcionamiento fundamental.

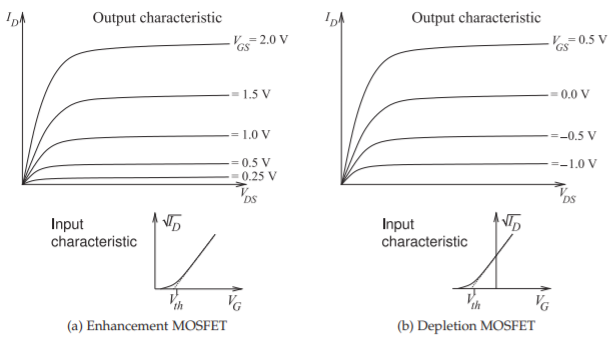

la terminal de la puerta. El término JFET se refiere más comúnmente a un FET de unión de silicio. Con semiconductores compuestos como GaAs, la unión pn de un JFET de silicio es reemplazada por una unión de barrera Schottky y el transistor se denomina FET metal-epitaxy-semiconductor (MESFET). Un dispositivo similar al MESFET es el transistor de alta movilidad electrónica (HEMT), donde el campo se establece en la unión de dos materiales semiconductores compuestos que tienen diferentes huecos de banda, llamados heterounión. El canal se forma en la heterounión. El HEMT también se denomina FET de heteroestructura (HFET). Un MESFET con una unión graduada se denomina FET dopado por modulación (MODFET). Un HEMT pseudomórfico (PhEMT) tiene una capa extremadamente delgada que establece el canal de manera que la estructura cristalina se estira y se establece una banda prohibida muy alta. Los JFET en modo de mejora y modo de agotamiento se contrastan en la Figura\(\PageIndex{6}\).

El modelo de transistor Materka-Kacprzak fue desarrollado para transistores MESFET de GaAs [14] pero también se utiliza para modelar transistores JFET y HEMT de silicio. El modelo se describe en la Sección 1.A.2 y la operación fundamental se describe mediante la Ecuación (1.A.44), la cual se repite aquí sin el área

Figura\(\PageIndex{6}\): Características de corriente-voltaje de JFET en modo de agotamiento y modo de mejora.

multiplicador:

\[\label{eq:20}I_{DS}=I_{DSS}\left[1+S_{S}\frac{V_{DS}}{I_{DSS}}\right]\left[1-\frac{V_{GS}(t-\tau )}{V_{P0}+\gamma V_{DS}}\right]^{(E+K_{E}V_{GS}(t-\tau ))}\times\tanh\left[\frac{S_{L}V_{DS}}{I_{DSS}(1-K_{G}V_{GS}(t-\tau ))}\right] \]

Aquí\(I_{DSS}\) está la corriente de saturación de drenaje, y esto, junto con todas las cantidades en la Ecuación\(\eqref{eq:20}\) distintas de\(V_{DS},\: V_{GS}\), y\(I_{DS}\) son constantes y especificadas como entradas por el usuario. La ecuación\(\eqref{eq:20}\) indica que la operación fundamental de un JFET es la de una fuente de corriente controlada por voltaje. Así, el modelo de circuito de señal pequeña de funcionamiento fundamental es como se muestra en la Figura\(\PageIndex{5}\) (b).

Los símbolos esquemáticos utilizados para el MESFET, HEMT y JFET se muestran en la Tabla\(\PageIndex{3}\). El único tipo MESFET utilizado, sin embargo, es el tipo n, ya que el ptype MESFET tiene un bajo rendimiento debido a la baja movilidad de los agujeros.

| Transistor | Símbolo IEEE | Símbolo de uso común |

|---|---|---|

| FET |  |

|

| FET, NJFET, MESFET, HEMT |  |

|

Tabla\(\PageIndex{3}\): Símbolos esquemáticos estándar IEEE para JFET (MESFET, HEMT, JFET) [8] y símbolos más utilizados en esquemas. Las letras indican terminales:\(\mathsf{G}\) (puerta),\(\mathsf{D}\) (drenaje),\(\mathsf{S}\) (fuente).

Notas al pie

[1] Una barrera Schottky ocurre en la interfaz abrupta entre un metal y un semiconductor dopado.

[2] La discusión es similar para un PMOSFET, pero con agujeros (portadores tipo p) formando el canal.

[3] La movilidad\(\mu\),, es la proporcionalidad de la velocidad de los portadores al campo eléctrico aplicado\(v_{d} = \mu E\), donde\(v_{d}\) está la velocidad promedio de deriva de los portadores y\(E\) es el campo eléctrico aplicado. La movilidad tiene las unidades\(\text{m}^{2}/(\text{V}\cdot\text{s})\), i.e\(\text{m}^{2}\cdot\text{V}^{−1}\cdot\text{s}^{−1}\).