3.11: Ejercicios

- Page ID

- 86057

\( \newcommand{\vecs}[1]{\overset { \scriptstyle \rightharpoonup} {\mathbf{#1}} } \) \( \newcommand{\vecd}[1]{\overset{-\!-\!\rightharpoonup}{\vphantom{a}\smash {#1}}} \)\(\newcommand{\id}{\mathrm{id}}\) \( \newcommand{\Span}{\mathrm{span}}\) \( \newcommand{\kernel}{\mathrm{null}\,}\) \( \newcommand{\range}{\mathrm{range}\,}\) \( \newcommand{\RealPart}{\mathrm{Re}}\) \( \newcommand{\ImaginaryPart}{\mathrm{Im}}\) \( \newcommand{\Argument}{\mathrm{Arg}}\) \( \newcommand{\norm}[1]{\| #1 \|}\) \( \newcommand{\inner}[2]{\langle #1, #2 \rangle}\) \( \newcommand{\Span}{\mathrm{span}}\) \(\newcommand{\id}{\mathrm{id}}\) \( \newcommand{\Span}{\mathrm{span}}\) \( \newcommand{\kernel}{\mathrm{null}\,}\) \( \newcommand{\range}{\mathrm{range}\,}\) \( \newcommand{\RealPart}{\mathrm{Re}}\) \( \newcommand{\ImaginaryPart}{\mathrm{Im}}\) \( \newcommand{\Argument}{\mathrm{Arg}}\) \( \newcommand{\norm}[1]{\| #1 \|}\) \( \newcommand{\inner}[2]{\langle #1, #2 \rangle}\) \( \newcommand{\Span}{\mathrm{span}}\)\(\newcommand{\AA}{\unicode[.8,0]{x212B}}\)

- Considere una línea de\(Z_{0} = 50\:\Omega\) transmisión de longitud\(\lambda /10\) en\(30\text{ GHz}\).

- Calcular los\(ABCD\) parámetros de la línea de transmisión en\(30\text{ GHz}\)?

- Con la línea de transmisión derivada por\(0.05\text{ pF}\) condensadores en cada extremo, calcule los\(ABCD\) parámetros de la línea de transmisión aumentada.

- En\(30\text{ GHz}\) la línea de transmisión aumentada es equivalente a una sola línea de transmisión con impedancia característica\(Z_{01}\) y longitud\(\ell_{1}\). ¿Qué es\(\ell_{1}\) en términos de longitudes de onda?

- ¿Qué es\(Z_{01}\)?

- Un amplificador FET distribuido de cuatro etapas como se muestra en la Figura 3.2.1 tiene\(R_{S} = R_{L} = 50\:\Omega\). Si se ignora la carga capacitiva y resistiva de los transistores, ¿cuáles son los valores óptimos de\(R_{1}\) y\(R_{2}\)? Proporcione su razonamiento.

- El amplificador FET distribuido de cuatro etapas que se muestra en la Figura 3.2.1 tiene\(R_{S} = 80\:\Omega\) y\(R_{L} = 25\:\Omega\). Si se ignora la carga capacitiva y resistiva de los transistores, ¿cuáles son los valores óptimos de\(R_{1}\) y\(R_{2}\)? Proporcione su razonamiento.

- La red de adaptación de entrada del amplificador de banda ancha considerada en la Sección 3.5 se muestra en la Figura 3.5.9 (b). (Tenga en cuenta que el puerto 2 de la red de entrada está conectado al transistor). Típicamente el conjugado complejo de la red\(S_{22}\) de entrada coincidiría con el coeficiente de reflexión de entrada\(\Gamma_{\text{in}}\),, del transistor. Pon tus respuestas en forma de ángulo de magnitud.

- Dibuja la red coincidente de entrada mostrando dónde\(S_{22}\) se determina. También dibuje el transistor terminado por la red de coincidencia de salida e indique dónde\(\Gamma_{\text{in}}\) se calcula.

- Utilice un simulador de microondas para calcular el\(S_{22}\) de la red de coincidencia de entrada en\(8, 9, ..., 12\text{ GHz}\).

- Determinar\(S_{22}^{\ast}\) la red de coincidencia de entrada en\(8, 9, ..., 12\text{ GHz}\).

- Determinar\(S_{11}\) el transistor en\(8, 9, ..., 12\text{ GHz}\).

- Determine\(\Gamma_{\text{in}}\) el transistor (terminado en la red de coincidencia de salida) en\(8, 9, ..., 12\text{ GHz}\).

- En una gráfica\(S_{22}^{\ast}\) de Smith de la red\(S_{11}\) de entrada, del transistor y\(\Gamma_{\text{in}}\) del transistor.

- Describa la condición de red coincidente de entrada para la transferencia de potencia máxima utilizada en el diseño del amplificador de banda estrecha.

- Discutir la falta\(\Gamma_{\text{in}}\) de coincidencia del transistor y\(S_{22}^{\ast}\) de la red de coincidencia de entrada. Describir el efecto que esto tiene en la respuesta de banda ancha del amplificador.

- La red de adaptación de salida del amplificador de banda ancha considerada en la Sección 3.5 se muestra en la Figura 3.5.10 (b). (Tenga en cuenta que el puerto 2 de la red de entrada está conectado al transistor). Típicamente el conjugado complejo de la red\(S_{22}\) de salida coincidiría con el coeficiente de reflexión de entrada\(\Gamma_{\text{out}}\),, del transistor. Pon tus respuestas en forma de ángulo de magnitud.

- Dibuje la red coincidente de salida mostrando dónde\(S_{22}\) se determina. También dibuje el transistor terminado por la red de coincidencia de entrada e indique dónde\(\Gamma_{\text{out}}\) se calcula.

- Utilice un simulador de microondas para calcular el\(S_{22}\) de la red de coincidencia de salida en\(8, 9, ..., 12\text{ GHz}\).

- Determinar\(S_{22}^{\ast}\) la red de coincidencia de salida en\(8, 9, ..., 12\text{ GHz}\).

- Determinar\(S_{22}\) el transistor en\(8, 9, ..., 12\text{ GHz}\).

- Determine\(\Gamma_{\text{out}}\) el transistor (terminado en la red de coincidencia de salida) en\(8, 9, ..., 12\text{ GHz}\).

- En una gráfica\(S_{22}^{\ast}\) de Smith de la red\(S_{22}\) de salida, del transistor y\(\Gamma_{\text{out}}\) del transistor.

- Describa la condición de red de coincidencia de salida para la transferencia de potencia máxima utilizada en el diseño del amplificador de banda estrecha.

- Discutir la falta\(\Gamma_{\text{out}}\) de coincidencia del transistor y\(S_{22}^{\ast}\) de la red de coincidencia de salida. Describir el efecto que esto tiene en la respuesta de banda ancha del amplificador. Usted querrá considerar el\(S_{21}\) del transistor.

- Trazar los\(S_{22}\) parámetros\(50\:\Omega\:S_{11}\) y de\(8\text{ GHz}\) a\(12\text{ GHz}\) del amplificador de banda ancha considerado en la Sección 3.5. Se verá que el amplificador no está emparejado a través de la banda. Discutir la razón por la que existe un desajuste aunque la ganancia y la cifra de ruido del amplificador, que se muestra en la Figura 3.6.1, son relativamente planas de\(8\text{ GHz}\) a\(12\text{ GHz}\). Tenga en cuenta que el Puerto 1 es el puerto de entrada del amplificador y el Puerto 2 es el Puerto de salida.

- La salida de un transistor se modela como la conexión en derivación de una fuente de corriente, una\(20\:\Omega\) resistencia, un\(0.35\text{ pF}\) condensador y un\(0.7\text{ nH}\) inductor.

- ¿Cuál es la admisión de la salida del transistor en\(8,\: 10,\) y\(12\text{ GHz}\)?

- ¿Cómo varía la susceptancia con la frecuencia?

- ¿Cuál es el elemento reactivo de derivación requerido para resonar la admitancia de salida del transistor en\(8,\: 10,\) y\(12\text{ GHz}\)?

- ¿Cuáles son las inductancias equivalentes requeridas para resonar la admitancia de salida del transistor a\(8,\: 10,\) y\(12\text{ GHz}\)?

- ¿Cómo varía la inductancia calculada en (d) con la frecuencia?

- Describir un circuito de dos elementos que tenga la característica identificada en (e). (Tenga en cuenta que este circuito solo sería capaz de lograr la característica requerida sobre un ancho de banda más pequeño que el requerido para una coincidencia de\(8\text{ GHz}\) a\(12\text{ GHz}\).)

- La salida de un transistor se modela como la conexión en derivación de una fuente de corriente, una\(68\:\Omega\) resistencia, un\(0.35\text{ pF}\) condensador y un\(0.7\text{ nH}\) inductor.

- ¿Cuál es la entrada de salida del transistor en\(8,\: 10\) y\(12\text{ GHz}\)?

- ¿Cómo varía la admisión con la frecuencia?

- Diseñe una red de coincidencia de elementos agrupados con dos elementos para hacer coincidir la salida del transistor\(10\text{ GHz}\) a una\(50\:\Omega\) fuente.

- Calcular la admitancia de entrada de la red coincidente, mirando desde el transistor, en\(8,\: 10,\) y\(12\text{ GHz}\).

- ¿Cuál es la admisión de entrada de una red de coincidencia ideal, mirando desde el transistor, en\(8,\: 10,\) y\(12\text{ GHz}\)? Trazar los loci de admisión real e ideal en una gráfica de Smith usando marcadores en\(8,\: 10,\)\(12\text{ GHz}\) e indicando la dirección de la frecuencia creciente con flechas.

- Consideremos un transistor que tenga los\(S\) parámetros mostrados en la Tabla 3.5.1 y la Figura 3.5.2 (a). Ignorar los efectos de retroalimentación y considerar que el coeficiente de reflexión que busca en la salida del transistor es\(S_{22}^{\ast}\).

- Dibuje y describa el problema de red de coincidencia de entrada de dos puertos con el Puerto 1 en la salida del transistor y una\(50\:\Omega\) terminación en el Puerto 2.

- ¿Cuál es el ideal\(S_{11}\) de la coincidencia de entrada de dos puertos en\(8\text{ GHz}\)?

- ¿Cuál es el ideal\(S_{11}\) de la coincidencia de entrada de dos puertos en\(10\text{ GHz}\)?

- ¿Cuál es el ideal\(S_{11}\) de la coincidencia de entrada de dos puertos en\(12\text{ GHz}\)?

- Trace el locus de\(8\text{ GHz}\) a\(12\text{ GHz}\)\(S_{11}\) de la entrada coincidente de dos puertos en un gráfico de Smith.

- Supongamos que el locus trazado en (e) de\(8\text{ GHz}\) a se\(12\text{ GHz}\) puede realizar usando una red de elementos agrupados. Comentar sobre la dificultad del diseño y el enfoque del diseño.

- En\(10\text{ GHz}\) un condensador,\(C_{1}\), tiene una reactancia de\(−50\:\Omega\).

- ¿Cuál es la impedancia de\(C_{1}\) at\(8,\: 10,\) y\(12\text{ GHz}\)?

- ¿Cómo\(C_{1}\) varía la impedancia de con la frecuencia?

- ¿Cuál es la inductancia requerida para resonar la capacitancia a\(8,\: 10,\) y\(12\text{ GHz}\)?

- ¿Cómo varía la inductancia calculada en (b) con la frecuencia?

- La entrada de un transistor se modela como una\(20\:\Omega\) resistencia en serie con un\(0.3\text{ pF}\) condensador.

- ¿Cuál es la impedancia de la entrada del transistor en\(8,\: 10,\) y\(12\text{ GHz}\)?

- ¿Cómo varía la impedancia con la frecuencia?

- ¿Cuál es la inductancia en serie requerida para resonar la capacitancia del transistor en\(8,\: 10,\) y\(12\text{ GHz}\)?

- Comente si se puede lograr una coincidencia de banda ancha de una fuente resistiva con la entrada de un transistor usando un inductor independiente de la frecuencia.

- La entrada de un transistor se modela como una\(20\:\Omega\) resistencia en serie con un\(0.3\text{ pF}\) condensador. El transistor es parte de un amplificador que opera en un\(50\:\Omega\) sistema.

- Diseñe una red de coincidencia de elementos agrupados con dos elementos (inductores y/o condensadores) para hacer coincidir la entrada del transistor\(10\text{ GHz}\) a una\(50\:\Omega\) fuente.

- Calcule la pérdida de retorno (buscando en la red coincidente desde la fuente) en\(8,\: 9,\: 10,\: 11,\) y\(12\text{ GHz}\).

- Calcule la fracción de la potencia de entrada disponible, expresada en decibelios, entregada al transistor en\(8,\: 9,\: 10,\: 11,\)\(12\text{ GHz}\) e indique la dirección de la frecuencia creciente con flechas.

- Comente sobre la variación en la ganancia del amplificador únicamente debido a la falta de coincidencia en la entrada del transistor.

- Considere la entrada de un transistor que tenga los\(S\) parámetros mostrados en la Tabla 3.5.1 y Figura 3.5.2 (a). Ignorar los efectos de retroalimentación para que para el dispositivo activo\(\Gamma_{\text{in}} = S_{11}\). También una red de coincidencia de entrada terminada\(50\:\Omega\) en el Puerto 1 y el dispositivo activo en el Puerto 2.

- ¿Cuál es el ideal\(50\:\Omega\: S_{22}\) de la red de coincidencia de entrada (es decir, vista desde la entrada del transistor) en\(8\text{ GHz}\)?

- ¿Cuál es el ideal\(50\:\Omega\: S_{22}\) de la red de coincidencia de entrada (es decir, vista desde la entrada del transistor) en\(10\text{ GHz}\)?

- ¿Cuál es el ideal\(50\:\Omega\: S_{22}\) de la red de coincidencia de entrada (es decir, vista desde la entrada del transistor) en\(12\text{ GHz}\)?

- Considera hacer coincidir la entrada de un transistor que tenga los\(S\) parámetros mostrados en la Tabla 3.5.1 y la Figura 3.5.2 (a). Ignorar los efectos de retroalimentación y considerar que el coeficiente de reflexión de entrada del transistor\(\Gamma_{\text{in}} = S_{11}\). La curva B en la Figura 3.5.2 (a) es el lugar de la impedancia que busca en la red coincidente desde el transistor. ¿Qué red de dos elementos tiene este locus? (Uno de los elementos puede ser una resistencia).

- Considere sintetizar una red coincidente de dos puertos terminada en una\(50\:\Omega\) carga y con un coeficiente de reflexión de entrada\(\Gamma_{1}\) mostrado como Curva B en la Figura 3.5.2 (a). Dibuje y describa el problema de red coincidente de dos puertos.

- Considere sintetizar una red coincidente de dos puertos terminada en una\(50\:\Omega\) carga y con un coeficiente de reflexión de entrada\(\Gamma_{1}\) mostrado como Curva B en la Figura 3.5.2 (a). ¿Se puede obtener una coincidencia de banda ancha usando una red coincidente de dos elementos? Explica tu respuesta en términos de rotaciones en un gráfico de Smith.

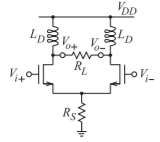

- Considere el amplificador de Clase A diferencial polarizado inductivamente que se muestra a continuación. \(L_{D}\)es un inductor de estrangulador así\(|sL| ≫ R_{L}\). [Parallels Ejemplo 3.6.1.]

Figura\(\PageIndex{1}\)

¿Cuál es el CMRR cuando\(R_{S} = 20\text{ k}\Omega,\: R_{L} = 10\text{ k}\Omega\), la transconductancia del transistor\(g_{m} = 50\text{ mS}\), y la resistencia drenaje-fuente,\(r_{d}\) es\(100\text{ k}\Omega\)?

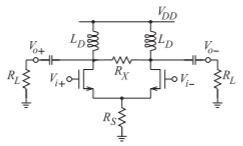

- Considere el amplificador de Clase A diferencial polarizado inductivamente que se muestra a continuación. Los condensadores se pueden tratar como cortocircuitos de RF. \(L_{D}\)es un inductor de estrangulador así\(|sL| ≫ R_{L}\). [Ejemplo de Parallels 3.6.1]

Figura\(\PageIndex{2}\)

- Derivar una expresión simbólica para el CMRR del amplificador asumiendo que la resistencia drenaje-fuente de los transistores,\(r_{0}\) o\(r_{d}\), es mucho mayor que ambos\(R_{L}\) y\(R_{X}\), y así se puede ignorar.

- ¿Cuál es el CMRR cuando\(R_{S} = 10\text{ k}\Omega,\)\(R_{X} = 30\text{ k}\Omega\),\(R_{L} = 10\text{ k}\Omega\), y la transconductancia del transistor,\(g_{m}\) es\(10\text{ mS}\).

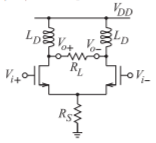

- Considere el amplificador de Clase A diferencial polarizado inductivamente que se muestra a continuación. \(L_{D}\)es un inductor de estrangulador así\(|sL| ≫ R_{L}\). [Ejemplo de Parallels 3.6.1]

Figura\(\PageIndex{3}\)

- Derivar una expresión simbólica para la ganancia de modo diferencial del amplificador.

- Derivar una expresión simbólica para el CMRR del amplificador.

- ¿Qué es CMRR cuando\(R_{S} = 10\text{ k}\Omega\),\(R_{L} = 10\text{ k}\Omega\), la transconductancia del transistor,\(g_{m}\) es\(15\text{ mS}\), y la resistencia drenaje-fuente de los transistores,\(r_{d}\), es\(100\text{ k}\Omega\)?

- Un amplificador diferencial tiene una ganancia de modo diferencial\(20\text{ dB}\) y una ganancia de modo común de\(−3\text{ dB}\).

- ¿Cuál es la ganancia en modo impares?

- ¿Cuál es la ganancia del modo pares?

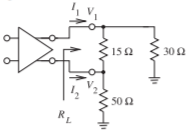

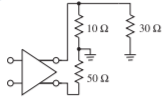

- Considera el amplificador diferencial a continuación. [Ejemplo de Parallels 3.6.1]

Figura\(\PageIndex{4}\)

- ¿Cuál es la impedancia de carga diferencial?

- ¿Cuál es la impedancia de carga en modo impares?

- ¿Cuál es la impedancia de carga de modo común?

- ¿Cuál es la impedancia de carga de modo par-modo?

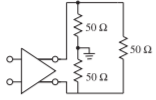

- Considera el amplificador diferencial a continuación. [Ejemplo de Parallels 3.6.1]

Figura\(\PageIndex{5}\)

- ¿Cuál es la impedancia de carga diferencial?

- ¿Cuál es la impedancia de carga en modo impares?

- ¿Cuál es la impedancia de carga de modo común?

- ¿Cuál es la impedancia de carga de modo par-modo?

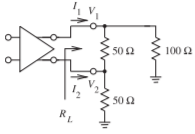

- Considera el amplificador diferencial a continuación. [Ejemplo de Parallels 3.6.1]

Figura\(\PageIndex{6}\)

- ¿Cuál es la impedancia de carga diferencial?

- ¿Cuál es la impedancia de carga en modo impares?

- ¿Cuál es la impedancia de carga de modo común?

- ¿Cuál es la impedancia de carga de modo par-modo?

- Si la ganancia de modo diferencial del amplificador es\(20\text{ dB}\) y la ganancia de modo común lo es\(2\text{ dB}\), ¿cuál es la ganancia en modo extraño?

- Considera el amplificador diferencial a continuación. \(L_{D}\)es un inductor de estrangulador así\(|sL| ≫ R_{L}\). [Ejemplo de Parallels 3.6.1]

Figura\(\PageIndex{7}\)

- ¿Cuál es la impedancia de carga diferencial?

- ¿Cuál es la impedancia de carga en modo impares?

- ¿Cuál es la impedancia de carga de modo común?

- ¿Cuál es la impedancia de carga de modo par-modo?

- Un amplificador pseudo-diferencial se muestra en la Figura 3.7.3. La polarización distribuida de este amplificador (reemplazando los inductores y\(R_{DD}\)), presenta una impedancia de modo común\(5\:\Omega\) y una impedancia de modo diferencial de\(1\text{ k}\Omega\) a los terminales de drenaje de los transistores en el medio de la banda del amplificador. La transconductancia de cada transistor es\(g_{m} = 1\text{ S}\), y los parásitos internos de los transistores pueden ser ignorados.

- Dibuje el esquema del amplificador de modo común sin los elementos de polarización. Incluya la resistencia de carga de modo común\(R_{Lc}\).

- Dibuje el esquema del amplificador de modo impar sin los elementos de polarización. Incluya la resistencia a la carga de modo impar\(R_{Lo}\).

- Dibuje el esquema del amplificador de modo par sin los elementos de polarización. Incluya la resistencia a la carga de modo impar\(R_{Lo}\).

- Dibuje el esquema del amplificador de modo diferencial sin los elementos de polarización. Incluya la resistencia de carga de modo común\(R_{Lc}\).

- ¿Cuál es la ganancia en modo común?

- ¿Cuál es la ganancia en modo diferencial?

- ¿Cuál es la relación de rechazo en modo común en decibelios?

- Un amplificador pseudo-diferencial se muestra en la Figura 3.7.3. La polarización distribuida de este amplificador (reemplazando los inductores y\(R_{DD}\)), presenta una impedancia de modo común\(5\:\Omega\) y una impedancia de modo extraño de\(1\text{ k}\Omega\) a los terminales de drenaje de los transistores en el medio de la banda del amplificador. La transconductancia de cada transistor es\(g_{m} = 100\text{ mS}\) y los parásitos internos de los transistores pueden ser ignorados.

- Dibuje el esquema del amplificador de modo común sin los elementos de polarización. Incluya la resistencia de carga de modo común\(R_{Lc}\).

- Dibuje el esquema del amplificador de modo impar sin los elementos de polarización. Incluya la resistencia a la carga de modo impar\(R_{Lo}\).

- Dibuje el esquema del amplificador de modo par sin los elementos de polarización. Incluya la resistencia a la carga de modo impar\(R_{Lo}\).

- Dibuje el esquema del amplificador de modo diferencial sin los elementos de polarización. Incluya la resistencia de carga de modo común\(R_{Lc}\).

- ¿Cuál es la impedancia de modo par que se presenta al amplificador?

- ¿Cuál es la impedancia de modo diferencial que se presenta al amplificador?

- ¿Cuál es la ganancia de voltaje de modo par-modo?

- ¿Cuál es la ganancia de voltaje en modo diferencial?

- ¿Cuál es la ganancia de voltaje en modo común?

- ¿Cuál es la ganancia de voltaje en modo impares?

- ¿Cuál es la relación de rechazo en modo común?

3.11.1 Ejercicios Por Sección

\(†\)desafiante,\(‡\) muy desafiante

\(§3.2\: 1†, 2, 3\)

\(§3.5\: 4‡, 5‡, 6†, 7†, 8†, 9†\)

\(§3.6\: 10, 11, 12, 13, 14, 15, 16†, 17†, 18†, 19†, 20, 21, 22, 23†, 24†\)

\(§3.7\: 25†, 26†\)

3.11.2 Respuestas a ejercicios seleccionados

- d)\(34.7\:\Omega\)

- b)\(121\)

- d)\(1/f^{2}\)

- c)

\(\begin{array}{l}{8\text{ GHz}, -2.77\text{ dB}}\\{9\text{ GHz}, -0.57\text{ dB}} \\ {10\text{ GHz}, 0\text{ dB}}\\{11\text{ GHz}, -0.33\text{ dB}}\\{12\text{ GHz}, -1.03\text{ dB}}\end{array}\)

- (h)\(-100\)

- b)\(-3\text{ dB}\)

- \(37.5\:\Omega\)

- a)

Figura\(\PageIndex{8}\)