4.10: Amplificadores de Potencia RFIC

- Page ID

- 86153

Una de las características distintivas del diseño RFIC es la síntesis de un circuito que intrínsecamente tiene los atributos deseados. Para un amplificador de potencia RFIC el circuito sintetizado debe producir bajos niveles de distorsión al tiempo que logra una alta eficiencia. El mecanismo de distorsión fundamental en un RFIC es la\(i-v\) característica casi cuadrática de un transistor MOS y la característica de transferencia tipo tanh de un amplificador MOS. Esta sección cuenta con tres ejemplos de técnicas analíticas y de circuitos para calcular y gestionar la distorsión en circuitos MOS.

4.10.1 Distorsión en una etapa de amplificador de potenciación-agotamiento MOSFET

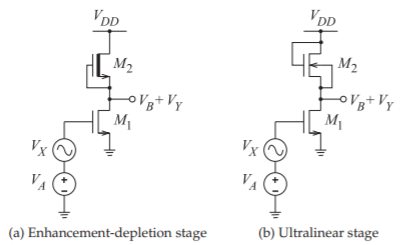

En esta sección, el análisis de series de potencia se aplica a la etapa de amplificador de aumento-agotamiento MOS que se muestra en la Figura\(\PageIndex{2}\) (a). Este circuito es un amplificador de Clase A con una etapa de ganancia de mejora de fuente común y un transistor de agotamiento como carga activa. Recordemos que con un MOSFET, la tensión del sustrato tiene un efecto importante en el funcionamiento del transistor. Con los transistores de modo de mejora, el sustrato o el cuerpo normalmente están conectados

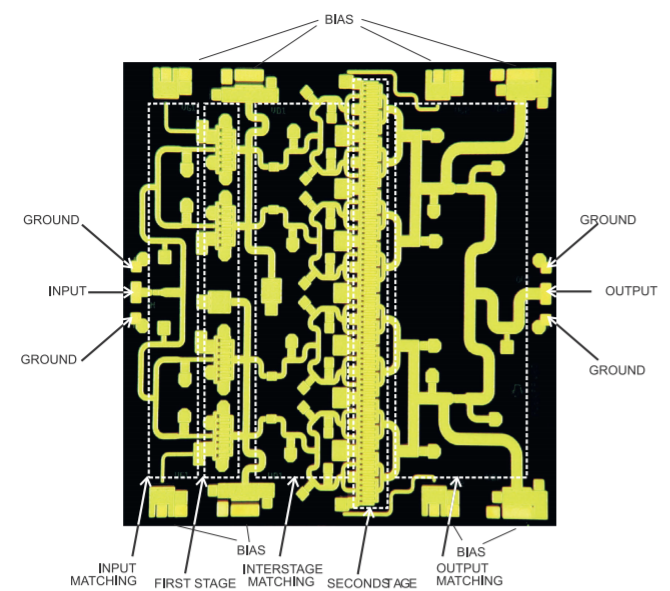

Figura\(\PageIndex{1}\): Amplificador\(8–12\text{ GHz}\) MMIC que produce aproximadamente\(1\text{ W}\) la potencia de salida con redes clave identificadas. (Cortesía Filtronic, PLC, usado con permiso.)

a la tensión más negativa en el circuito, en este caso tierra. Entonces, como\(M_{1}\) tiene el cuerpo conectado a la fuente, no hay efecto corporal para\(M_{1}\). No obstante, para\(M_{2}\) el efecto corporal se debe considerar. Usando una simple relación cuadrática entrada-salida MOSFET,

\[\label{eq:1}I_{D1}=\frac{K_{1}}{2}(V_{A}+V_{X}-V_{T0E})^{2}=I_{D2}=\frac{K_{2}}{2}\left(-V_{TD}^{2}\right) \]

donde el voltaje umbral de\(M_{2}\), con el efecto corporal, es

\[\begin{align}V_{TD}&=V_{T0D}+\gamma\left(\sqrt{2\phi_{F}+V_{B}+V_{Y}}-\sqrt{2\phi_{Y}}\right)\nonumber \\ \label{eq:2}&=V_{1}+\gamma\left(\sqrt{2\phi{F}+V_{B}+V_{Y}}\right)\end{align} \]

(Estas ecuaciones se dan en forma ligeramente diferente en la Sección 1.A.1. Las cantidades\(\phi_{F}\) y\(\phi_{Y}\) son potenciales de inversión incorporados.) También\(K\) es proporcional a\(W/L\), donde\(W\) está el ancho del canal del transistor y\(L\) es su longitud. Se\(V_{1} = V_{T0D} − \gamma\sqrt{2\phi_{Y}}\) ha introducido la variable, pero como se verá se cancelará durante la derivación.

El objetivo aquí es desarrollar una relación entre la señal de entrada\(V_{X}\) y la señal de salida\(V_{Y}\). El primer paso para desarrollar una relación simple que pueda usarse en el diseño inicial es relacionar los niveles de voltaje del punto de operación. Reordenando la ecuación\(\eqref{eq:1}\),

\[\label{eq:3}\sqrt{\frac{K_{1}}{K_{2}}}(V_{A}+V_{X}-V_{TOE})=-V_{TD} \]

con la elección apropiada de la señal hecha. Combinación de ecuaciones\(\eqref{eq:1}\) y\(\eqref{eq:2}\) rendimientos

\[\begin{align}\label{eq:4}\sqrt{\frac{K_{1}}{K_{2}}}(V_{A}+V_{X}-V_{TOE})&=-\left(V_{1}+\gamma\sqrt{2\phi_{F}+V_{B}+V_{Y}}\right) \\ \label{eq:5}\text{and }\sqrt{\frac{K_{1}}{K_{2}}}(V_{X})+\sqrt{\frac{K_{1}}{K_{2}}}(V_{A}-V_{TOE})&=-\left(V_{1}+\gamma\sqrt{2\phi_{F}+V_{B}+V_{Y}}\right)\end{align} \]

Ahora\(V_{X} =0= V_{Y}\), cuando, es decir, cuando no hay señal de CA, la ecuación\(\eqref{eq:5}\) se convierte

\[\label{eq:6}\sqrt{\frac{K_{1}}{K_{2}}}(V_{A}-V_{TOE})=-\left(V_{1}+\gamma\sqrt{2\phi_{F}+V_{B}}\right) \]

Sustitución de\(\eqref{eq:5}\) rendimientos de ecuación\(\eqref{eq:6}\) en ecuación

\[\begin{align}\label{eq:7}\sqrt{\frac{K_{1}}{K_{2}}}V_{X}&=\gamma\sqrt{2\phi_{F}+V_{B}}-\gamma\sqrt{2\phi_{F}+V_{B}+V_{Y}}\\ \label{eq:8}\left(\sqrt{\frac{K_{1}}{K_{2}}}V_{X}-\gamma\sqrt{2\phi_{F}+V_{B}}\right)^{2}&=\gamma^{2}(2\phi_{F}+V_{B}+V_{Y}) \\ \label{eq:9}\frac{K_{1}}{K_{2}}V_{X}^{2}-\left(2\gamma\sqrt{\frac{K_{1}}{K_{2}}}\sqrt{2\phi_{F}+V_{B}}\right)V_{X}+\gamma^{2}(2\phi_{F}+V_{B})&=\gamma^{2}V_{Y}+\gamma^{2}(2\phi_{F}+V_{B})\end{align} \]

Figura\(\PageIndex{2}\): Etapas del amplificador MOS.

y finalmente

\[\label{eq:10}\left(\frac{K_{1}}{K_{2}}\right)V_{X}^{2}-\left(2\gamma\sqrt{\frac{K_{1}}{K_{2}}}\sqrt{2\phi_{F}+V_{B}}\right)V_{X}=\gamma^{2}V_{Y} \]

Por lo tanto, el componente de la salida que difiere del punto de reposo es

\[\label{eq:11}V_{Y}=\frac{-2}{\gamma}\sqrt{\frac{K_{1}}{K_{2}}}\sqrt{2\phi_{F}+V_{B}}V_{X}+\frac{1}{\gamma^{2}}\frac{K_{1}}{K_{2}}V_{X}^{2} \]

Para una entrada sinusoidal\(V_{X} = |V_{X}| \cos(\omega t)\),\(V_{X}^{2} =\frac{1}{2}|V_{X}|^{2} +\frac{1}{2} |V_{X}|^{2} \cos(2\omega t)\), que contiene el segundo armónico de la señal de entrada.

Entonces el nivel de distorsión del segundo armónico\(_{2}\), HD, la relación entre el componente de\(V_{Y}\) segundo armónico y el componente fundamental, es

\[\begin{align}\text{HD}_{2}&=\left(\left|\frac{1}{2}\frac{K_{1}}{K_{2}}\frac{1}{\gamma^{2}}V_{X}^{2}\right|\right)\left(\left|\frac{-2\sqrt{2\phi_{F}+V_{B}}}{\gamma}\sqrt{\frac{K_{1}}{K_{2}}}V_{X}\right|\right)^{-1}\nonumber \\ \label{eq:12}&=\frac{1}{4\gamma\sqrt{2\phi_{F}+V_{B}}}\sqrt{\frac{K_{1}}{K_{2}}}|V_{X}|\end{align} \]

Examen de Ecuaciones\(\eqref{eq:11}\) y\(\eqref{eq:12}\) lleva a las siguientes conclusiones. Si hay mucha ganancia de voltaje (\(∝\sqrt{K_{1}/K_{2}}\)), entonces el nivel de la señal de entrada debe ser pequeño para mantener baja la distorsión armónica. Otras consideraciones de diseño que tienen el mismo efecto son utilizar un dispositivo más ancho, lo que aumenta la transconductancia (ya que\(g_{m}\approx K ∝ W/L\)) del transistor para que la corriente de drenaje se mantenga para los niveles de voltaje de entrada más bajos. Por supuesto, hacer que el dispositivo sea más ancho aumenta los parásitos capacitivos, lo que reducirá la frecuencia máxima de operación. Hacer que el canal del dispositivo sea más corto también aumenta la transconductancia sin afectar el rendimiento de la frecuencia. El punto importante es que existen compensaciones en la modificación del rendimiento del circuito y éstas solo se hacen evidentes utilizando el tipo de análisis que aquí se presenta. El uso del análisis y la optimización del diseño a través de la síntesis es una de las piedras angulares del diseño RFIC. En gran parte esto es posible debido a las características de corriente-voltaje de tipo cuadrático (blando) de los MOSFET.

4.10.2 Distorsión en la conexión MOS Ultralineal

El circuito de la Figura\(\PageIndex{2}\) (b) es una etapa de ganancia en modo de mejora con una carga en modo de mejora. Transistor\(M_{2}\) es la carga de mejora de canal n con su pozo atado a su fuente. Es decir, en la fabricación de\(M_{2}\), se forma un pozo y el transistor se construye en el pozo. El pozo ahora sirve como sustrato para\(M_{2}\). Dado que el pozo y la fuente de\(M_{2}\) están conectados entre sí, no\(M_{2}\) está sujeto al efecto corporal. Una propiedad importante de este circuito es que las características de\(M_{1}\) y\(M_{2}\) son coincidentes. Utilizando un enfoque similar al utilizado en la sección anterior, se puede desarrollar la relación entrada/salida del circuito. Equiparar las corrientes de drenaje,

\[\label{eq:13}I_{D1}=\frac{K_{1}}{2}(V_{A}+V_{X}-V_{T0E})^{2}=I_{D2}=\frac{K_{2}}{2}(V_{DD}-V_{B}-V_{Y}-V_{T0E})^{2} \]

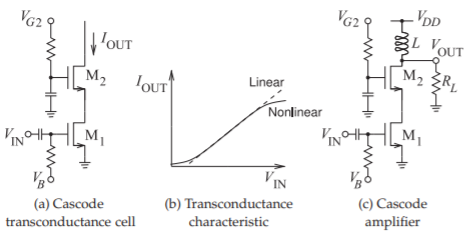

Figura\(\PageIndex{3}\): Un amplificador cascode MOS. \(L\)es un inductor de estrangulación y es un circuito abierto de RF. \(V_{B}\)y\(V_{G2}\) son voltajes de polarización. La celda de transconductancia cascode se utiliza en esta sección como una celda tanh cascode (TCC).

Con

\[\label{eq:14}V_{X}=V_{Y}=0,\qquad\sqrt{\frac{K_{1}}{K_{2}}}(V_{A}-V_{T0E})=V_{DD}-V_{B}-V_{T0E} \]

Por lo tanto

\[\label{eq:15}\sqrt{\frac{K_{1}}{K_{2}}}V_{X}+(V_{DD}-V_{B}-V_{T0E})=(V_{DD}-V_{B}-V_{Y}-V_{T0E}) \]

y así

\[\label{eq:16}V_{Y}=-\sqrt{\frac{K_{1}}{K_{2}}}V_{X} \]

El resultado es que, siempre que los transistores estén emparejados, el amplificador es inherentemente lineal. Entonces dentro de las aproximaciones de las expresiones de corriente de drenaje no hay distorsión, y esto incluye ninguna distorsión de intermodulación de tercer orden o rebrote espectral.

4.10.3 Amplificadores de potencia RFIC con distorsión mínima

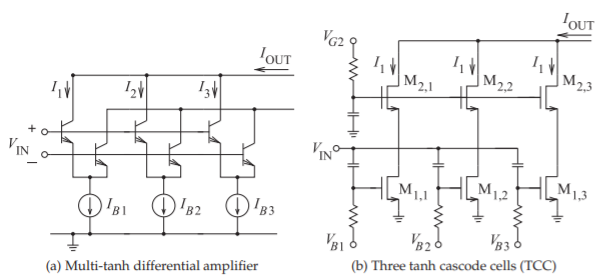

La estrategia lineal por diseño más utilizada para el diseño de amplificadores RFIC lineales es usar lo que se llama el método multi-tanh [66]. La idea es escalar varias etapas de amplificador paralelo para obtener una característica lineal global. Consideremos el amplificador cascode MOS mostrado en la Figura\(\PageIndex{3}\) (c), el cual se basa en la celda de transconductancia mostrada en la Figura\(\PageIndex{3}\) (a). Al aplicar un voltaje de entrada\(V_{\text{IN}}\),, se produce una corriente de salida\(I_{\text{OUT}}\),, con la característica tanh-like mostrada en la Figura\(\PageIndex{3}\) (b). Esta característica es la causa dominante de distorsión de amplitud en un amplificador FET. La estrategia de diseño para linealizar la característica de salida de un amplificador FET es poner múltiples etapas de amplificador en paralelo para que la característica general de corriente-voltaje combine de manera óptima la característica similar al tanh de cada etapa.

La figura\(\PageIndex{4}\) muestra dos circuitos que explotan la estrategia multi-tanh. La Figura\(\PageIndex{4}\) (a) es una celda de transconductancia de amplificador diferencial multitanh de tres etapas en la que las corrientes de polarización\(I_{B1},\: I_{B2},\) y se\(I_{B3}\) ajustan de manera que la característica global de entrada/salida\(V_{\text{IN}}\),\(I_{\text{OUT}}\) versus, tenga mayor linealidad que la de las etapas individuales [66]. Un concepto similar se utiliza para combinar la salida de múltiples etapas de cascode (ver Figura\(\PageIndex{4}\) (b)) y esta es una topología más adecuada para el desarrollo de amplificadores de potencia RFIC [67].

Como ejemplo del uso del enfoque de diseño multi-tanh, considere el amplificador cascode de tanh múltiple en la Figura\(\PageIndex{4}\) (b) con tres celdas tanh cascode (TCC). Este amplificador tiene distorsión tanto de amplitud como de fase. La distorsión de amplitud es el resultado en gran medida de la corriente-tensión tipo tanh-like

Figura\(\PageIndex{4}\): Combinar la salida de múltiples etapas para obtener una característica de transconductancia global altamente lineal.

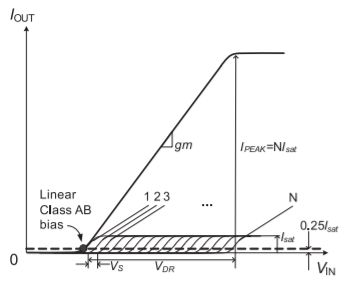

Figura\(\PageIndex{5}\): Combinar la salida de las etapas de cascode\(N\) Clase AB para obtener una característica de transconductancia global altamente lineal. Se muestran las\(V_{\text{IN}}\) características individuales\(I_{\text{OUT}}\) versus de cada uno de\(N\) los transistores, cada uno polarizado de manera diferente. La\(V_{\text{IN}}\) característica combinada\(I_{\text{OUT}}\) versus es la suma de los transistores individuales\(I_{\text{OUT}}\) After [67].

característica de las etapas individuales de cascode. La distorsión de fase es el resultado en gran medida de la no linealidad de la capacitancia de puerta de los FET. La característica tanh de cada celda tanh cascode en la Figura\(\PageIndex{4}\) (b) se ajusta escalando los transistores\(M_{1,1},\: M_{1,2},\) y\(M_{1,3}\), y cambiando sus voltajes de polarización\(V_{B1},\: V_{B2},\) y\(V_{B3}\). El enfoque de diseño se ilustra en la Figura\(\PageIndex{5}\) y se presenta un enfoque de síntesis en las referencias [68] y [67]. Cada etapa tanh cascode opera en modo AB de clase alta y con sesgo apropiado las características de tanh son escalonadas. Tenga en cuenta que para señales de entrada pequeñas solo están activas una o unas pocas etapas. Las corrientes de cada etapa se suman para producir una respuesta global de transconductancia linealizada.

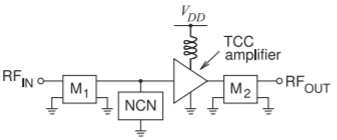

La distorsión de fase se reduce mediante el uso de un circuito de predistorsión analógica que realiza una red de capacitancia no lineal que cancela la capacitancia de puerta no lineal combinada de las etapas de cascode. La topología completa del amplificador de potencia CMOS RF se muestra en la Figura\(\PageIndex{6}\), donde NCN es la red de condensadores no lineales. La micrografía de este amplificador se muestra en la Figura

Figura\(\PageIndex{6}\): Amplificador de potencia RFIC completo con un amplificador TCC con 12 celdas TCC Clase AB y una red de condensadores no lineales (NCN) y redes de coincidencia de entrada y salida (\(\text{M}_{1}\)y\(\text{M}_{2}\)). Después [67].

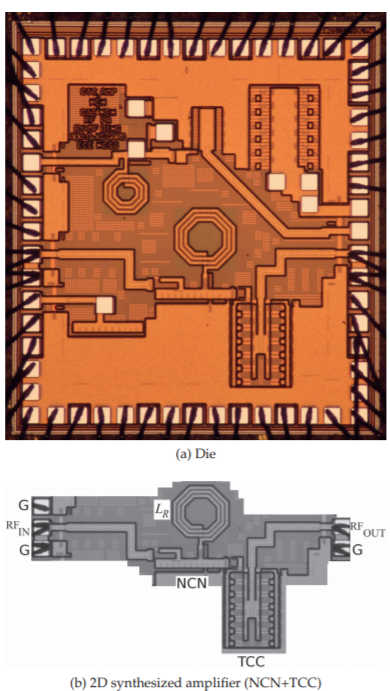

Figura\(\PageIndex{7}\): Micrografía de matriz del amplificador sintetizado 2D con etapa de amplificador de celda tanh cascode (TCC) y etapa de red de condensadores no lineales (NCN). (Hay dos operando a diferentes frecuencias, una en la parte superior de la matriz y otra en la parte inferior. Aquí se hace referencia al de abajo.) El dado también contiene un amplificador TCC, una red NCN y un amplificador RF CMOS Clase AB convencional. El suministro es\(3.6\text{ V}\) y la conexión a tierra es identificada por\(\mathsf{G}\). El dado se muestra en (a) y el amplificador sintetizado 2D en (b). El inductor\(L_{R}\) resuena la componente lineal de la capacitancia NCN y la componente lineal de la capacitancia de puerta del amplificador TCC. Las redes coincidentes y el inductor de coque\(V_{DD}\) están fuera de chip.

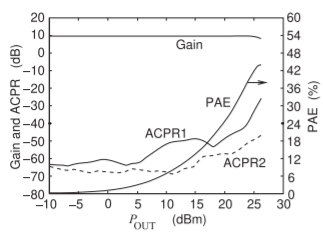

\(\PageIndex{7}\)(a) junto con los circuitos de prueba. El amplificador TCC con la red de condensadores no lineales se desglosa en la Figura\(\PageIndex{7}\) (b). El rendimiento del amplificador de potencia RFIC tiene un excelente rendimiento, como se muestra en la Figura\(\PageIndex{8}\), y logra una potencia de salida de\(25\text{ dBm}\) con una eficiencia de\(42\%\) y un ACPR de\(−22\text{ dBc}\).

Figura\(\PageIndex{8}\): Rendimiento del amplificador TCC con el circuito de predistorsión de condensador no lineal\(960\text{ MHz}\) con una señal de prueba WCDMA. Una ganancia de\(9.4\text{ dB}\) con eficiencia de potencia agregada de\(41.6\%\) se logra con una potencia de salida de\(24.9\text{ dBm}\) y cumpliendo con las especificaciones 3G ACPR1\(−33\text{ dBc}\) y un ACPR2 de\(−43\text{ dBc}\). Después [67].