3.1: Descripción general del formato de instrucciones de código de máquina

- Page ID

- 80657

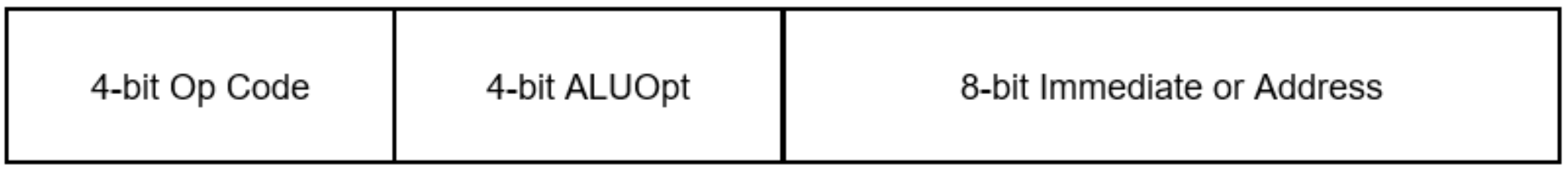

Todas las instrucciones de código de máquina para nuestra computadora consistirán en dos segmentos de 4 bits y un segmento de 8 bits, como se muestra a continuación.

El primer segmento de 4 bits representará el tipo de operación. Los posibles tipos de operaciones son los siguientes:

- 1 —Este opcode representa una operación inmediata que utiliza la ALU para producir un resultado. Esta instrucción consiste en el código de operación de 4 bits, una opción ALU de 4 bits (ALUOpt) para decirle a la ALU qué operación ejecutar, y un valor inmediato de datos de 8 bits para un operando. Según se implementa la ALU solo ejecuta 2 operaciones, 0x0 es sumar y 0x1 es restar, aunque los ejercicios al final del texto agregan más operaciones. Se pueden implementar un máximo de 16 operaciones en la CPU.

A continuación se muestran ejemplos de traducción de estas instrucciones de montaje en código de máquina.

La instrucción:

addi 2

se traduce en el siguiente código de máquina:

0x1002

La instrucción:

subi 15

se traduce al siguiente código de máquina

0x110f

- 2 — Este opcode representa una operación de dirección de memoria que utiliza la ALU para producir un resultado. Esta instrucción consiste en el código de operación de 4 bits, un AluOpt de 4 bits para decirle a la ALU qué operación ejecutar, y una dirección de memoria de datos de 8 bits para un operando. Según se implementa la ALU solo ejecuta 2 operaciones, 0x0 es sumar y 0x1 es restar, aunque los ejercicios al final del texto agregan más operaciones. Se pueden implementar un máximo de 16 operaciones en la CPU.

A continuación se muestran ejemplos de traducción de estas instrucciones de montaje en código de máquina.

La instrucción:

add 2

se traduce en el siguiente código de máquina:

0x2002

La instrucción

sub 15

se traduce en el siguiente código de máquina

0x210f

Tenga en cuenta que durante el proceso de ensamblaje las etiquetas en el código de ensamblaje se traducen en direcciones, por lo que las etiquetas nunca aparecerán en el código

- 3 — Este opcode ejecuta la operación clac (por ejemplo, establece el

$acen 0). En esta instrucción se ignoran todos los bits posteriores después del 0x3, por lo que pueden contener cualquier valor. Por convención, los bits adicionales siempre deben establecerse en 0.Por ejemplo, las siguientes instrucciones de montaje

clac

se traduce en

0x3000

- 4 — Este opcode ejecuta la operación stor. En esta instrucción no se utiliza el ALU opt de 4 bits, y debe establecerse en 0. El valor de la dirección es la dirección en la que almacenar el valor en el

$ac. Por ejemplo, la siguiente instrucciónstor 15

se traduce en:

0x400f

- 0x5 — El opcode ejecuta la operación beqz. En esta instrucción no se utiliza la operación ALU de 4 bits, y se debe poner en blanco. El resultado de esta operación es que

$pcse establece en el valor de dirección si el$aces cero. Establecer el valor para el$pchace que el programa se ramifique a esa dirección.Por ejemplo, la siguiente instrucción

beqz 40

se traduce en:

0x5028