7.1: Velocidad y potencia en circuitos CMOS

- Page ID

- 84459

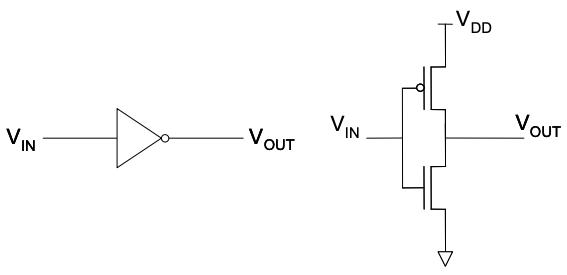

Como debes recordar de 6.002, el circuito CMOS arquetipo se muestra en la Figura 7.2.1. Está compuesto por dos FET complementarios: el MOSFET superior está apagado para una entrada de alto voltaje, y el MOSFET inferior está apagado dado una entrada baja. El circuito es un inversor.

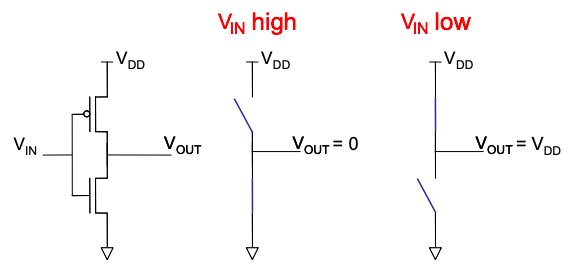

Para la entrada de voltaje constante, el circuito tiene dos estados estables, como se muestra en la Figura 7.2.2. Debido a que uno de los transistores siempre está apagado en estado estacionario, el circuito idealmente no tiene disipación de potencia estática.

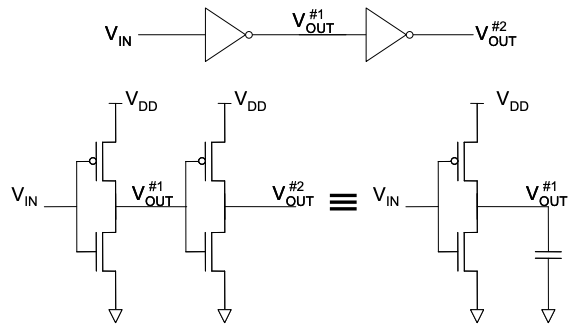

Pero cuando el voltaje de entrada cambia el circuito disipa brevemente la energía. Esto se conoce como el poder dinámico. Modelamos la dinámica de un circuito CMOS como se muestra en la Figura 7.2.3. En este arquetipo de circuito CMOS se utiliza un inversor para accionar más puertas CMOS. Para encender y apagar las compuertas posteriores, el inversor debe cargar y descargar condensadores de compuerta. Así, modelizamos la carga de salida del primer inversor mediante un condensador.

Ahora consideramos las características clave de rendimiento de la electrónica CMOS.

El producto de retardo de energía (PDP)

El producto de retardo de potencia mide la energía disipada en un circuito CMOS por operación de conmutación. Dado que la energía por evento de conmutación es fija, el PDP describe una compensación fundamental entre la velocidad y la disipación de potencia: si operamos a altas velocidades, disiparemos mucha energía.

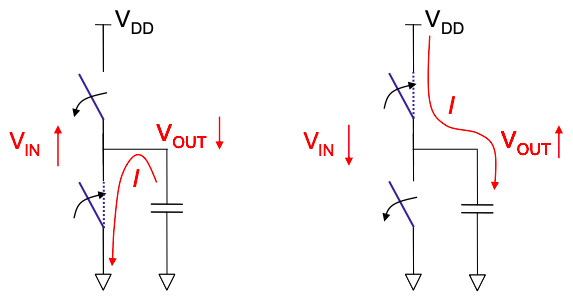

Imagine una transición de entrada de alta a baja al inversor de la Figura 7.2.1

Si el condensador de salida está inicialmente descargado, la energía disipada en el FET PMOS viene dada por:

\[ W = \int^{\tau/2}_{0} dt(V_{DD}-V_{OUT})I \nonumber \]

La corriente en el condensador viene dada por:

\[ I = C\frac{dV_{OUT}}{dt}, \nonumber \]

Combinando estas expresiones:

\[ W = \int^{\tau/2}_{0} dt(V_{DD}-V_{OUT})\frac{dV_{OUT}}{dt} = C\int^{V_{DD}}_{0} dV_{OUT}(V_{DD}-V_{OUT}) = \frac{1}{2}CV_{DD}^{2} . \nonumber \]

De igual manera, en la segunda mitad del ciclo, cuando el condensador se descarga a través del FET NMOS, es sencillo volver a mostrarlo\(W = \frac{1}{2}CV_{DD}^{2}\). Así, la energía disipada por ciclo es:

\[ PDP = CV_{DD}^{2} . \nonumber \]