7.3: Límites de escalado en CMOS

- Page ID

- 84482

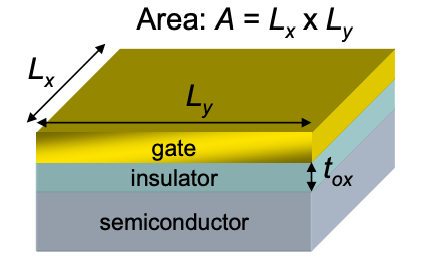

La ecuación\ ref {7.2.4} demuestra la importancia de la capacitancia de la puerta. La capacitancia es

\[ C = \frac{\varepsilon A}{t_{ox}} \nonumber \]

donde A es el área de la sección transversal del condensador,\(t_{ox}\) es el grosor del aislador de puerta y\(\varepsilon\) es su constante dieléctrica.

Ahora bien, si reducimos todas las dimensiones por un factor s (s<1), la capacitancia disminuye:

\[ C(s) = \frac{\varepsilon s^{2} A}{st_{ox}} = sC_{0} \label{7.3.1} \]

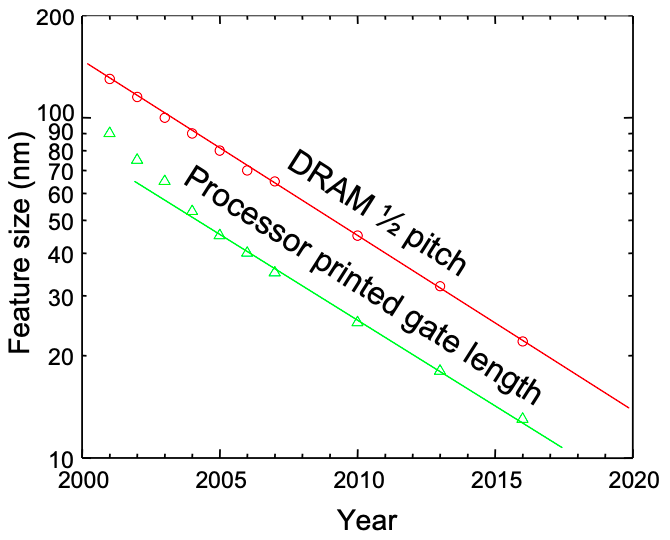

A partir de la ecuación\ ref {7.2.4}, las reducciones en C reducen el PDP, permitiendo que los circuitos funcionen más rápido para una disipación de potencia dada. De hecho, los avances en el desempeño de la electrónica han llegado en gran parte a través de un esfuerzo continuo de los ingenieros para reducir el tamaño de los transistores, reduciendo así la capacitancia y el PDP; ver Figura\ PageIndex {2}.

En la actualidad, sin embargo, hay crecientes preocupaciones de que nos estamos acercando al final de nuestra capacidad para escalar componentes electrónicos. Hay al menos dos problemas que se avecinan en la electrónica:

Control electrostático deficiente

Vimos en la parte 5 que el control de puerta sobre la carga en el canal requiere\(t_{ox} \ll L\), donde L es la longitud del canal. Ahora como la longitud del canal,,\(L \rightarrow 10\ nm\), es decir\(t_{ox} \rightarrow 1\ nm\), ¡el aislador de puerta es solo de varios átomos de espesor! Pero el campo eléctrico al otro lado de la puerta debe permanecer alto para inducir carga en el canal. Por lo tanto, las reducciones en los tamaños de las características eventualmente impondrán severas demandas al aislador de puerta.

Densidad de potencia

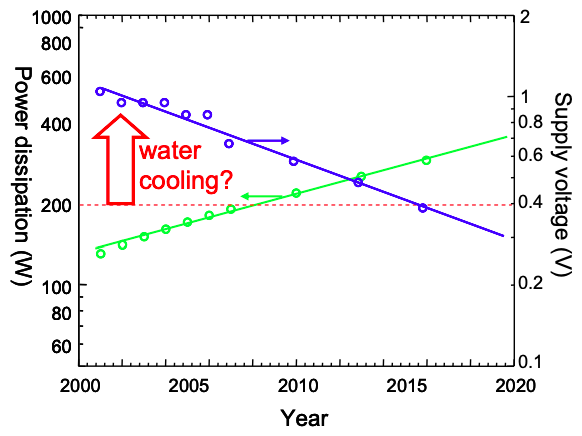

El problema electrostático es fundamental, pero es posible que las preocupaciones de energía puedan obstruir el escalado de los circuitos CMOS antes de la aparición de problemas electrostáticos. La densidad de potencia es una preocupación particular, ya que no se beneficia de las continuas reducciones en el tamaño de los componentes. Si las dimensiones de un MOSFET se reducen por un factor s (s<1),\(C \propto s\) (recuerde que la capacitancia es proporcional al área de la sección transversal, e inversamente proporcional al espaciamiento entre las cargas). Pero incluso si el PDP escala como s, la densidad de potencia puede aumentar debido a que el número de dispositivos por unidad de área aumenta a medida que\(1/s^{2}\).

Las densidades de potencia de los circuitos integrados típicos se acercan a las de un filamento de bombilla (~ 100 W/cm2). A modo de comparación, la densidad de potencia de la superficie del sol es de ~ 6000 W/cm2. La eliminación del calor generado por un circuito integrado se ha convertido quizás en la restricción crucial para el rendimiento de la electrónica moderna. De hecho, el límite fundamental para la densidad de potencia parece ser aproximadamente 1000 W/cm2. En la práctica, utilizando la refrigeración por agua de un sustrato de Si calentado uniformemente con microcanales incrustados, se ha logrado una densidad de potencia de 790 W/cm2 con una temperatura del sustrato cercana a la temperatura ambiente.

Como es evidente a partir de la Ecuación\ ref {7.2.4} anterior, el PDP también depende de la tensión de alimentación\(V_{DD}\). Asegurando que la potencia total disipada por chip\ ll 200 W ha pasado\(V_{DD}\) de 5V en los primeros circuitos CMOS a casi 1V hoy en día. Si la industria se ajusta a las predicciones de la hoja de ruta, el voltaje de suministro eventualmente alcanzará 0.4V para 2016.

Pero, ¿cuál es el límite último para el PPD?