8.2: Diagrama de circuito para un MUX

- Page ID

- 82815

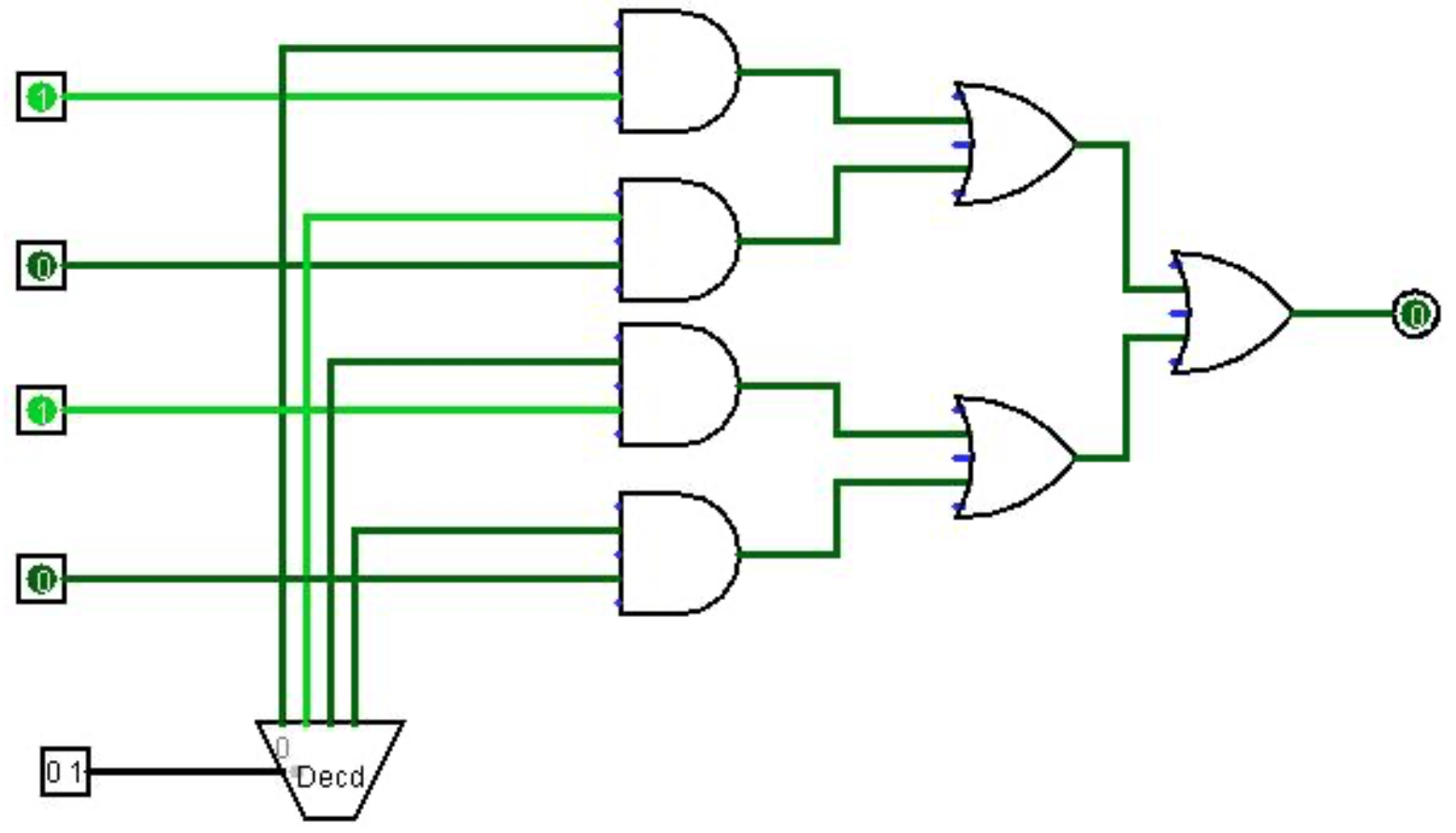

La tabla de verdad en la Figura 8.1.2 caracteriza un MUX de 4 a 1.

Usando esta tabla de verdad, el MUX 4 a 1 se puede construir usando al darse cuenta de que I 0 solo se selecciona cuando S 1 S 0 son 00, I 1 solo se selecciona con S 1 S 0 son 01, etc. así el bit I 0 se puede enviar a una puerta AND con el resultado de la valor invertido de S 1 y S 0. Esta puerta AND siempre será 0 excepto cuando S 1 S 0 son 00, cuando será I 0. De esta manera I 1, I 2 e I 3 pueden ser seleccionados por una operación AND con 01, 10 y 11 respectivamente.

Tenga en cuenta que solo se puede seleccionar un valor de entrada para cualquier valor de S 0 S 1. La única entrada que se envía a una puerta AND con 1 será 0 o 1, en función de su entrada. El resultado de todas las puertas AND se envían a una puerta OR de 4 vías. Recordar 0 + X es siempre X, el resultado de la puerta OR representará la entrada seleccionada. Puede ser 0 o 1, pero será 0 o 1 basado en el valor de la entrada seleccionada.

El esquema de un MUX se da en la Figura\(\PageIndex{1}\).

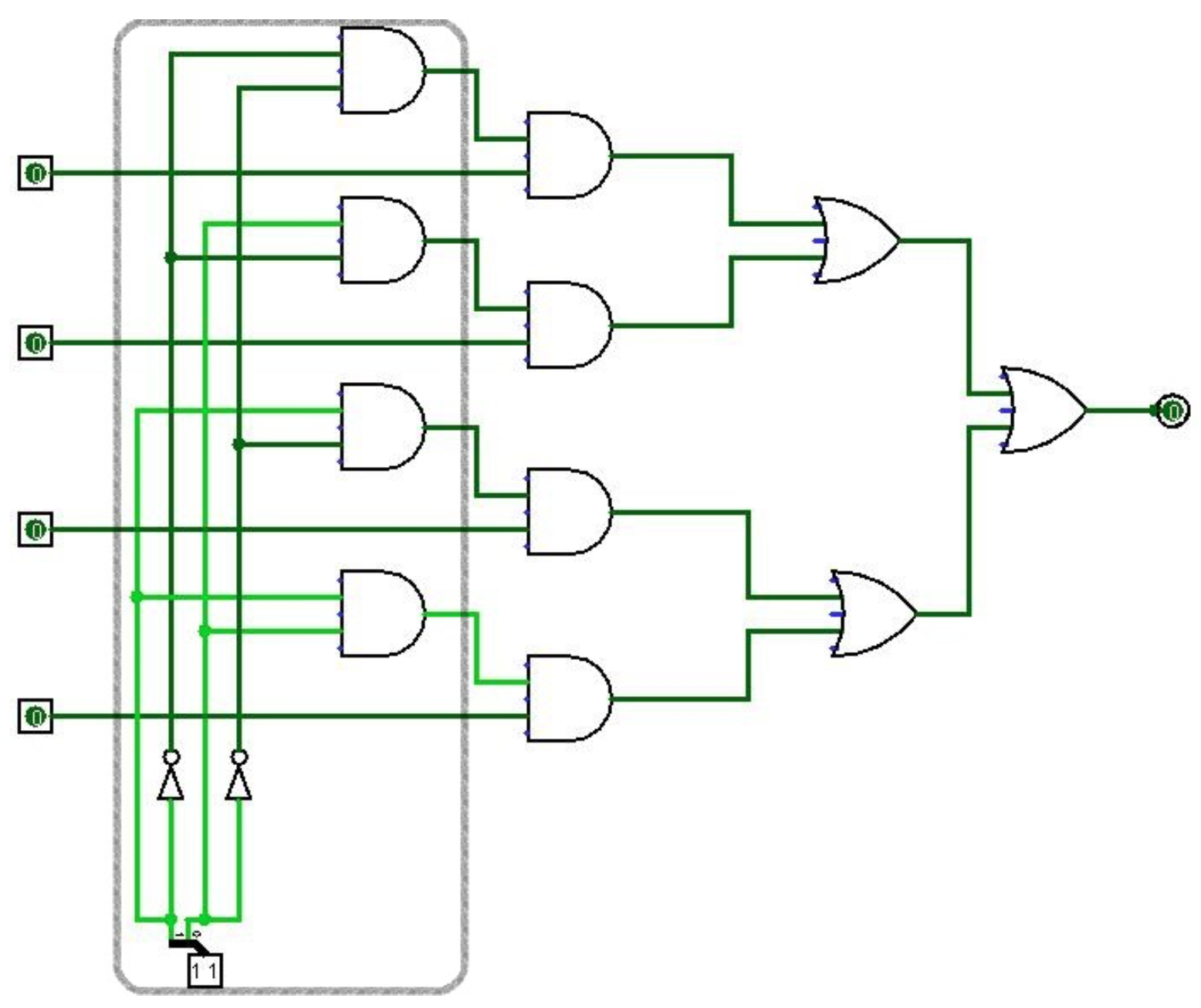

Algo interesante de este circuito es que se implementa un decodificador como parte del circuito multiplexor, como se muestra en la parte esbozada de la Figura\(\PageIndex{1}\). Esto sugiere otra forma de implementar el MUX usando un decodificador para seleccionar qué línea de entrada seleccionar. Esto se muestra en la Figura\(\PageIndex{2}\). Haremos uso de esto en el diseño de nuestra implementación de un MUX.