9.4: flip-flop activado por el borde

- Page ID

- 82715

Un flip-flop activado por borde (o simplemente flip-flop en este texto) es una modificación del pestillo que permite que el estado solo cambie durante un pequeño período de tiempo cuando el pulso de reloj está cambiando de 0 a 1. Se dice que se dispara en el borde del pulso de reloj, y así se llama flip-flop activado por bordes. El flip-flop puede ser activado por un borde de elevación (0->1, o gatillo de borde positivo) o borde descendente (1->0, o gatillo de borde negativo). Todas las chanclas en este texto serán gatillo de borde positivo.

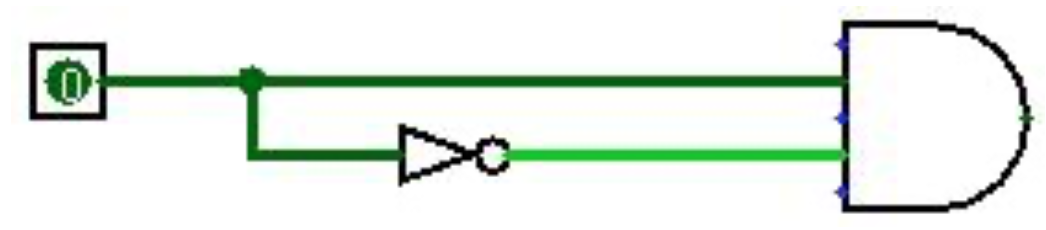

El concepto detrás de un flip-flop es que la corriente que fluye dentro de un circuito no es instantánea, sino que siempre tiene un retraso corto dependiendo del tamaño del circuito, las puertas que debe atravesar, etc. Esto se ilustra en la Figura\(\PageIndex{1}\). En este diagrama, parecería que la ecuación booleana (true^false) siempre es falsa, por lo que este circuito siempre debe producir una salida 0. Sin embargo, dado que hay un pequeño pero presente retraso en la corriente que pasa por la puerta NOT, hay un período de tiempo pequeño pero finito en el que las dos entradas a la puerta AND serían ambas 1 (cuando el reloj está transitando de 0 a 1), y la salida del circuito sería 1.

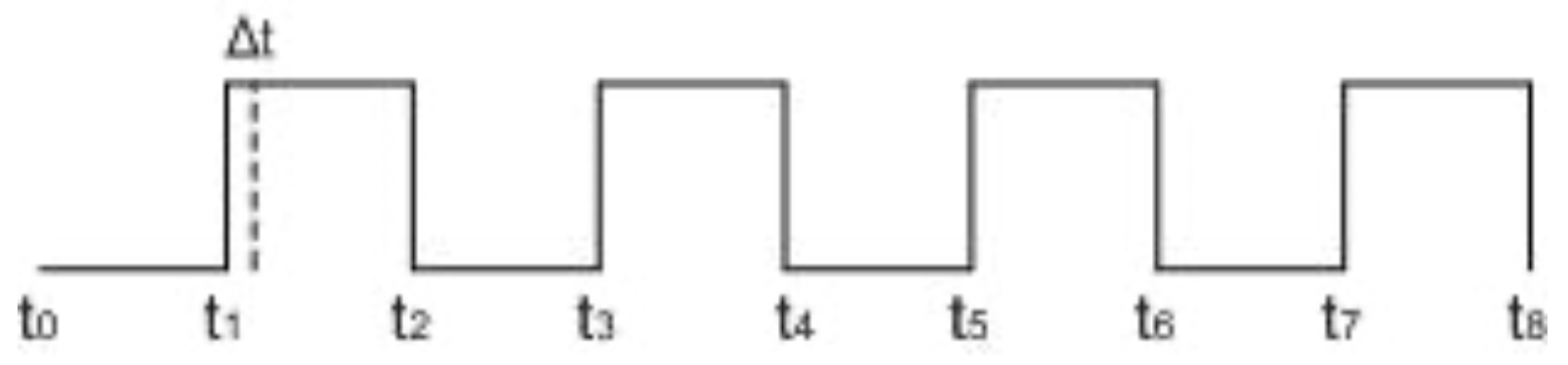

Esta cantidad de tiempo, Δt, se muestra en el diagrama de onda cuadrada en la Figura\(\PageIndex{2}\). Este tiempo se llama un disparador de borde de elevación, y es durante este intervalo de tiempo que el circuito anterior sería 1.

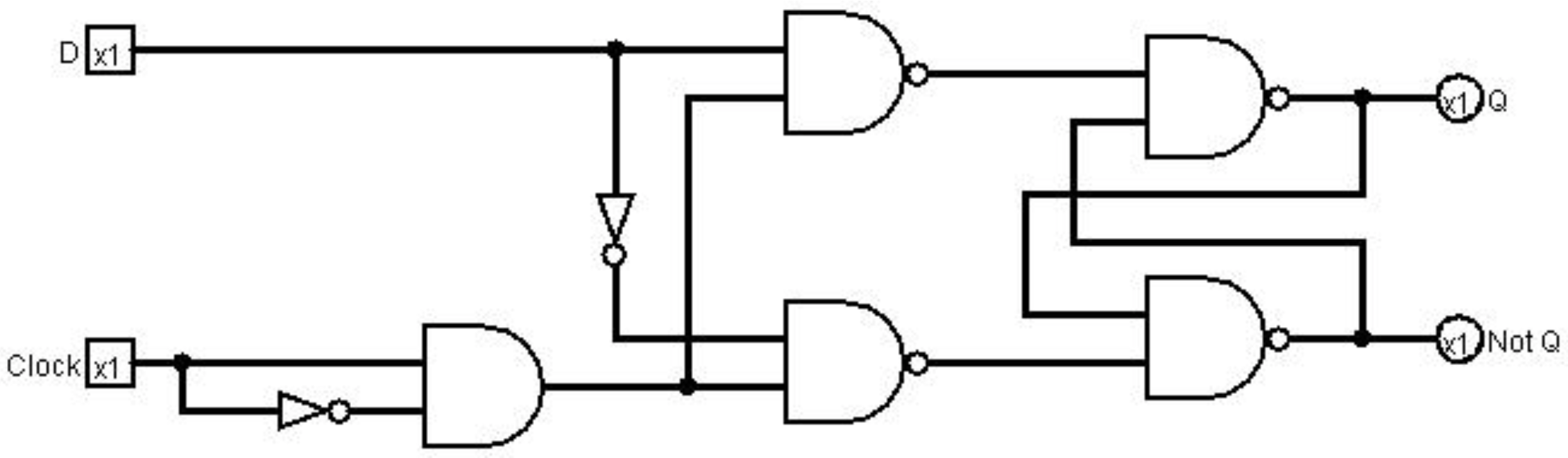

Este retardo corto se puede utilizar para cambiar el circuito de tal manera que solo cambiará durante este breve disparador de borde. Debido a que Δt es más pequeño que cualquier lógica combinacional, esto elimina la necesidad de crear un segundo pestillo para mantener un estado válido. Un circuito que implementa este concepto se muestra en la Figura\(\PageIndex{3}\).

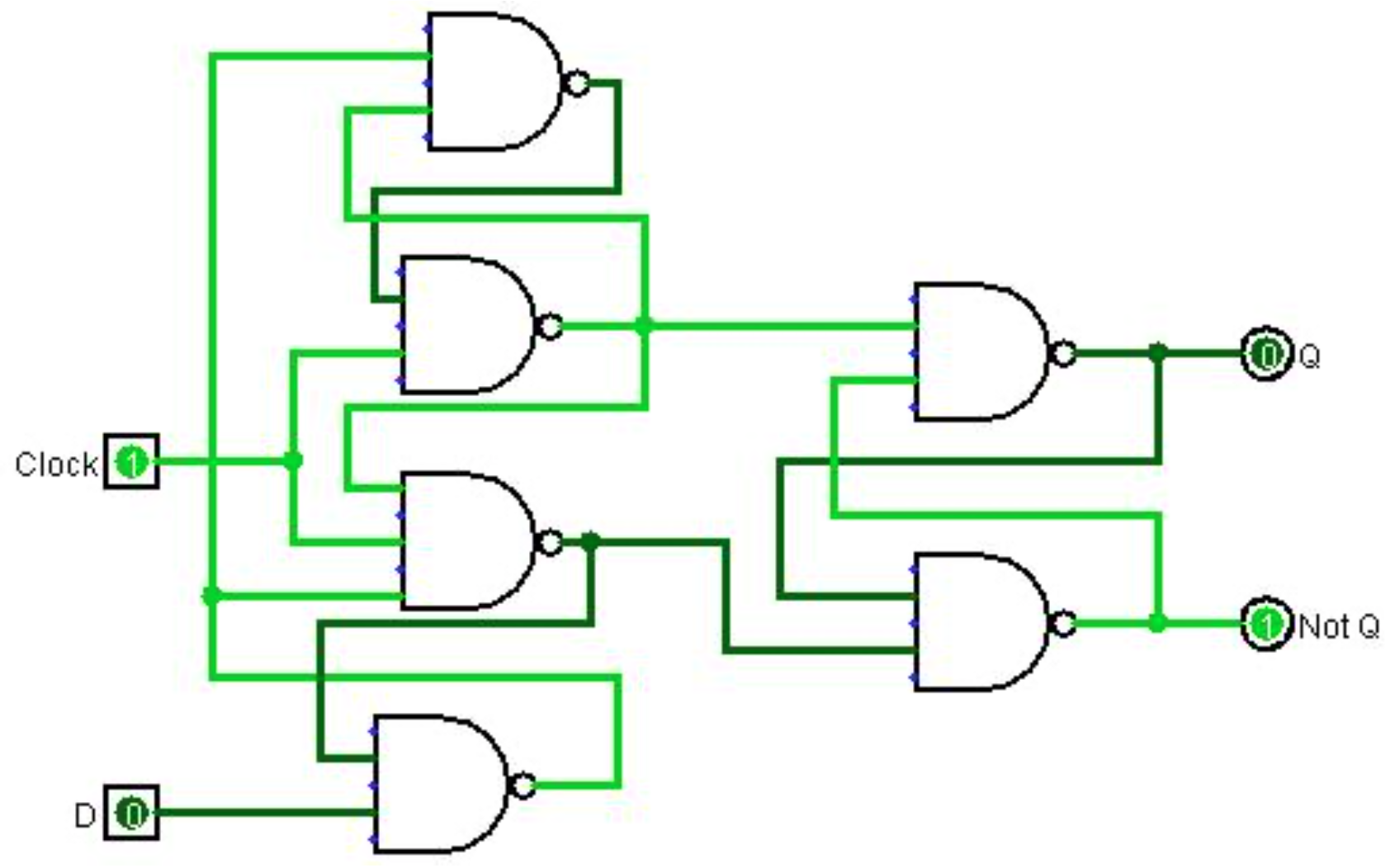

El problema con el circuito en la Figura\(\PageIndex{3}\) es que no puede garantizar que el retardo de tiempo causado por el disparador de borde sea suficiente para permitir que la lógica de cierre obtenga el estado correcto. El circuito en la Figura\(\PageIndex{4}\) es una verdadera implementación de un flip-flop. Si bien parece mucho más complejo que la implementación en la Figura\(\PageIndex{3}\), se deja como un ejercicio para mostrar que contiene exactamente el mismo número de puertas que el ejemplo anterior.

Debido a un problema conocido como debouncing, es difícil ilustrar un flip-flop aisladamente como circuito. Por lo que este capítulo no implementará un flip-flop. Sin embargo, se utilizará un flip-flop como parte de los circuitos del capítulo 10.