6.9: Bucle de Fase Bloqueada (PLL)

- Page ID

- 85271

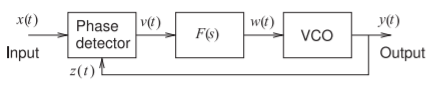

Figura\(\PageIndex{1}\): Un bucle de fase bloqueada con un detector de fase y un divisor de frecuencia indicado por\((1/N)\).

Un bucle de bloqueo de fase (PLL) es un sistema de retroalimentación en el que la frecuencia y fase de una señal de salida está relacionada con la frecuencia y fase de una señal de entrada. El diagrama de bloques de un PLL se muestra en la Figura\(\PageIndex{1}\). Una señal de entrada\(x(t)\) se compara con una señal de retroalimentación\(z(t)\). La frecuencia de\(y(t)\) será la frecuencia promedio de\(x(t)\). La forma en que el bucle logra esto es que la salida del detector de fase es proporcional a la diferencia de fase de\(x(t)\) y\(z(t)\). Esto luego es filtrado por el bloque\(F(s)\) (generalmente un filtro de paso bajo) para producir una señal similar a CC que impulsa un VCO. El bloque de filtrado\(F(s)\),, elimina componentes no deseados del detector de fase y también establece la respuesta dinámica del PLL.

6.9.1 Operación

El funcionamiento del PLL en la Figura se\(\PageIndex{1}\) puede modelar como un sistema lineal con la suposición de que\(x(t)\) y\(z(t) (= y(t)\) aquí) son señales casi periódicas. Por lo tanto, aproximadamente

\[\label{eq:1}x(t)=A_{x}\cos(\omega_{x}t+\phi_{x})\quad\text{and}\quad z(t)=A_{w}\cos(\omega_{z}t+\phi_{z}) \]

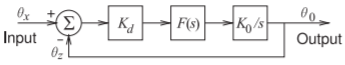

Figura\(\PageIndex{2}\): Modelo linealizado de un bucle analógico de bloqueo de fase.

Los PLL requieren que la frecuencia de radián\(\omega_{x}\) esté cerca de\(\omega_{z}\), que está cerca de la frecuencia de funcionamiento libre del VCO. (En la práctica,\(\omega_{x}\) suele ser mucho menor que\(\omega_{z}\) y se utiliza un divisor de frecuencia para dividir la señal\(\omega_{z}\) a para obtener una señal con una frecuencia cercana a\(\omega_{x}\). El análisis es similar al que aquí se presenta). Esto define el rango de captura del PLL. Por lo tanto, la ecuación se\(\eqref{eq:1}\) puede escribir

\[\label{eq:2}x(t)=A_{x}\cos(\Theta_{x}(t))\quad\text{and}\quad z(t)=A_{w}\cos(\Theta_{0}(t)) \]

Las fases\(\Theta_{x}\) e\(\Theta_{0}\) incorporan las fases originales\(\phi_{x}\) y\(\phi_{w}\), respectivamente, y la diferencia de fase efectiva dependiente del tiempo debido a la pequeña diferencia dependiente del tiempo de las frecuencias de\(x(t)\) y\(z(t)\). El análisis del PLL en la Figura\(\PageIndex{1}\) comienza con el voltaje en la salida del detector de fase\(v(t)\), que es proporcional a la diferencia de fase de las dos señales de entrada e independiente de su amplitud:

\[\label{eq:3}v(t)=K_{d}(\Theta_{x}-\Theta_{0}) \]

donde\(K_{d}\) está el factor de ganancia del detector de fase. La salida del detector de fase es filtrada por el bloque con función de transferencia\(F(s)\). Por lo general este bloque es un filtro de paso bajo, pero hay aplicaciones donde podría ser un filtro de paso de banda o tener alguna otra característica.

La salida del VCO es controlada por el voltaje que\(w(t)\) produce una señal con frecuencia

\[\label{eq:4}f_{0}=f_{c}+\Delta f = f_{c}+K_{0}v(t) \]

donde\(f_{c}\) es la frecuencia de oscilación cuando el voltaje de control es cero y\(K_{0}\) es el factor de ganancia VCO.

Ecuaciones\(\eqref{eq:3}\) y\(\eqref{eq:4}\) describir el sistema lineal mostrado en la Figura\(\PageIndex{2}\). La función de transferencia de este sistema es

\[\label{eq:5}\frac{\theta_{0}}{\theta_{x}}=\frac{K_{d}K_{0}F(s)/s}{1+K_{d}K_{0}F(s)/s}=\frac{G(s)}{1+G(s)} \]

donde\(G(s) = K_{d}K_{0}F(s)\). La función de error de fase es

\[\label{eq:6}\epsilon(s)=\theta_{x}(s)-\theta_{0}=\theta_{x}\left[1-\frac{K_{d}K_{0}F(s)}{s+K_{d}K_{0}F(s)}\right]=\frac{s\theta_{x}(s)}{s+K_{d}K_{0}F(s)} \]

Por lo que la función de error de fase está directamente relacionada con la fase de la señal de entrada\(x(t)\). En la siguiente sección se utiliza una elección particular de la función\(F(s)\) de transferencia, lo que lleva a la identificación de una aplicación PLL particular.

6.9.2 PLL de primer orden

Sin un filtro (es decir,\(F(s) = 1\)) el PLL se conoce como un PLL de primer orden o bucle de primer orden y su función de transferencia es

\[\label{eq:7}\frac{\theta_{0}(s)}{\theta_{x}(0)}=\frac{K_{d}K_{0}/s}{1+K_{d}K_{0}/s}=\frac{K_{d}K_{0}}{s+K_{d}K_{0}} \]

Esta parece ser la función de transferencia de un filtro de paso bajo, pero la entrada al sistema es de fase y la salida es la desviación de fase de la frecuencia de funcionamiento libre del VCO. La función de error de fase del PLL de primer orden es

\[\label{eq:8}\epsilon (s)=\theta_{x}(s)-\theta_{0}=\theta_{x}(s)\left(1-\frac{K_{d}K_{0}}{s+K_{d}K_{0}}\right)=\frac{s\theta_{x}(s)}{s+K_{d}K_{0}} \]

Ahora se derivará la respuesta de estado estacionario del PLL de primer orden a señales de entrada específicas. El comportamiento a largo plazo (estado estacionario) se desarrolla utilizando el teorema del valor final. Una función\(H(s)\) con todos los polos en el plano de la mitad izquierda tiene una respuesta de dominio de tiempo\(h(t)\) con un comportamiento a largo plazo dado por

\[\label{eq:9}\lim_{t\to\infty}h(t)=\lim_{s\to 0}sH(s) \]

Consideremos ahora la respuesta a un cambio de paso,\(\Delta\theta_{x}\), de la fase de la señal de entrada. La transformada de Laplace de una función escalonada de magnitud\(\Delta\theta_{x}\) es\(\Delta\theta_{x}/s\) y esto es lo que se utiliza en la Ecuación\(\eqref{eq:8}\). Por lo tanto, la función de error de estado estacionario,\(\epsilon_{ss} = \epsilon (t)\) como\(t\to\infty\), es

\[\begin{align}\epsilon_{ss}&=\lim_{s\to 0}\left[\frac{s^{2}\theta_{x}(s)}{s+K_{d}K_{0}}\right]=\lim_{s\to 0}\left[\frac{s^{2}\Delta\theta_{x}/s}{s+K_{d}K_{0}}\right]=\lim_{s\to 0}\left[\frac{s\Delta\theta_{x}}{s+K_{d}K_{0}}\right]\nonumber \\ \label{eq:10}&=0\end{align} \]

La ecuación\(\eqref{eq:10}\) indica que un PLL de primer orden eventualmente rastreará un cambio de fase de la señal de entrada. Sin embargo, no responderá inmediatamente ya que el bucle tiene una característica de paso bajo. En efecto, el PLL está actuando como un filtro de\(Q\) paso de banda alto.

Ahora considere un cambio de paso en la frecuencia de la señal de entrada. Si el cambio de paso en la frecuencia radián de\(x(t)\) es\(\Delta\omega_{x}\), entonces el cambio de fase resultante será una rampa para que, en el dominio de Laplace,\(\theta (s)=\Delta\omega_{x}/s^{2}\). Entonces el error de estado estacionario es

\[\begin{align}\epsilon_{ss}&=\lim_{s\to 0}\left[\frac{s^{2}\Delta\omega_{x}/s^{2}}{s+K_{d}K_{0}}\right] = \lim_{s\to 0}\left[\frac{\Delta\omega_{x}}{s+K_{d}K_{0}}\right]\nonumber \\ \label{eq:11}&=\Delta\omega_{x}/(K_{d}K_{0})\end{align} \]

La ecuación\(\eqref{eq:11}\) indica que un PLL de primer orden seguirá un cambio en la frecuencia con un error de fase que es proporcional a la magnitud del cambio de frecuencia. Entonces, si la señal de entrada\(x(t)\) es una señal modulada en frecuencia, el PLL de primer orden demodulará la señal y recuperará la modulación original como señal de error. Así, un PLL de primer orden demodula una señal de FM, es decir, es un demodulador de frecuencia.

6.9.3 Aplicaciones

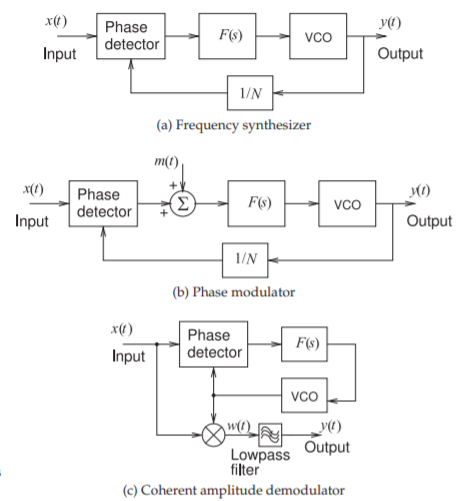

En la Figura se muestran tres aplicaciones del PLL\(\PageIndex{3}\). Se utiliza un sintetizador de frecuencia para crear una señal bloqueada a un oscilador de referencia de frecuencia fija y muy preciso pero a otra frecuencia (ver Figura\(\PageIndex{3}\) (a)). Normalmente la referencia es un oscilador de referencia de baja frecuencia de precisión, como un oscilador de cristal de cuarzo [36]. La frecuencia de salida no está a la misma frecuencia que el oscilador de referencia. Esto se logra mediante la inclusión de un divisor de frecuencia en el PLL. Normalmente el factor de división,\(N\), es un entero

Figura\(\PageIndex{3}\): Aplicaciones que utilizan bucles de fase bloqueada.

de manera que la frecuencia de la señal de salida será un múltiplo entero de la frecuencia de entrada. Un sintetizador fraccionario de\(N\) frecuencia se logra usando dos divisores enteros con factores de división\(N\) y\(M\). Un controlador alterna entre los dos factores de división de manera que el VCO tiende a emitir primero una frecuencia y luego la siguiente. El VCO se estabiliza a una frecuencia que es el promedio ponderado de los dos factores de división. Si la frecuencia se divide\(M\) por un tiempo\(\tau_{M}\), luego\(N\) por el tiempo\(\tau_{N}\), y se repite, entonces el factor de división efectivo es\((\tau_{M}M + \tau_{N}N)/(\tau_{M} +\tau_{N})\). La dinámica de bucle (determinada por el filtro\(F(s)\)) se elige para que el VCO solo pueda cambiar más lentamente que la alternancia de los factores de división. Los factores de división, y la alternancia entre sus dos valores, se eligen para sintetizar una señal de salida con la frecuencia deseada.

La segunda aplicación del PLL es un modulador de fase, ver Figura\(\PageIndex{3}\) (b). La señal moduladora de fase se suma\(m(t)\) efectivamente al error de fase generado por el detector de fase. Esto da como resultado un cambio en la fase de la salida del VCO compensando el cambio de fase insertado.

La tercera aplicación del PLL es el demodulador de amplitud coherente mostrado en la Figura\(\PageIndex{3}\) (c). La entrada es una señal modulada en amplitud

\[\label{eq:12}x(t)=A[1+m(t)]\sin(\omega_{0}t) \]

que se desmodula para recuperarse\(m(t)\) multiplicando\(x(t)\) por una señal LO con la misma frecuencia portadora. La característica de\(F(s)\) se elige para que el PLL genere la señal LO a medida que el bucle establece la oscilación

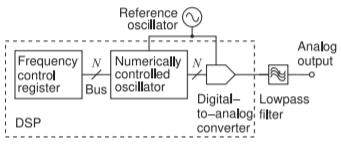

Figura\(\PageIndex{4}\): Módulo de síntesis digital directa (DDS).

frecuencia como la frecuencia central de la entrada modulada. El filtro de bucle\(F(s)\) asegura que la frecuencia de VCO no puede cambiar demasiado rápido y la frecuencia de salida del VCO se aproxima a una señal sinusoidal que tiene una frecuencia de radián\(\omega_{0}\) con un desplazamiento de fase. Por lo tanto

\[\label{eq:13} w(t)=x(t)\sin(\omega_{0}t+\theta)=A[1+m(t)]\frac{1}{2}[\cos\theta -\cos(2\omega_{0}t_{\theta})] \]

Después del filtrado de paso bajo, la salida es

\[\label{eq:14}y(t)=A[1+m(t)]\cos\theta \]

Con la dinámica de bucle elegida para que\(\theta\) sea pequeña, se recupera la modulación original\(m(t)\),,. Este demodulador AM funciona bien cuando la SNR de entrada es baja ya que la demodulación es coherente.