3.5: Puertas TTL NAND y AND

- Page ID

- 154403

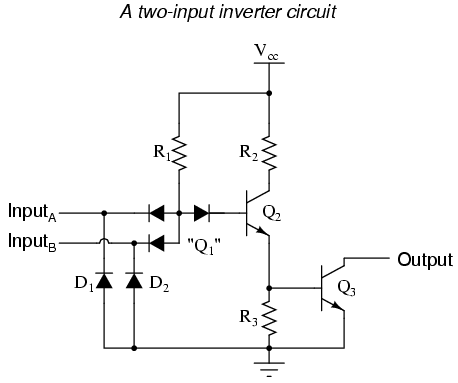

Supongamos que alteramos nuestro circuito básico inversor de colector abierto, agregando un segundo terminal de entrada igual que el primero:

Este esquema ilustra un circuito real, pero no se le llama “inversor de dos entradas”. A través del análisis, descubriremos cuál es la función lógica de este Circuito y, en consecuencia, cómo debe designarse.

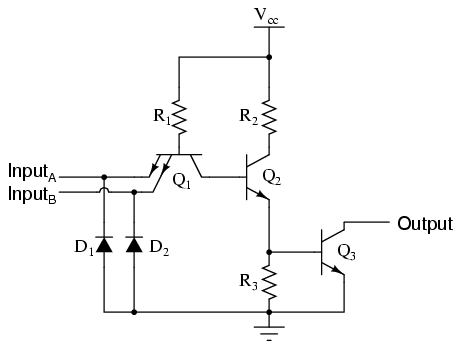

Al igual que en el caso del inversor y el búfer, el clúster de diodos “de dirección” marcado como “Q 1” en realidad se forma como un transistor, aunque no se usa en ninguna capacidad de amplificación. Desafortunadamente, una estructura de transistor NPN simple es inadecuada para simular las tres uniones PN necesarias en esta red de diodos, por lo que se necesita un transistor (y símbolo) diferente. Este transistor tiene un colector, una base y dos emisores, y en el circuito, se ve así:

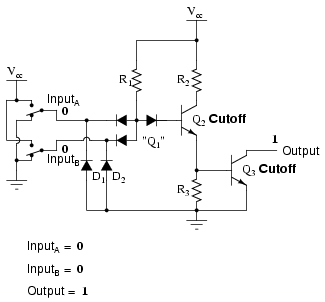

En el circuito de entrada única (inversor), poner a tierra la entrada resultó en una salida que asumió el estado “alto” (1). En el caso de la configuración de salida de colector abierto, este estado “alto” era simplemente “flotante”. Permitir que la entrada flote (o estar conectada a V cc) resultó en que la salida se pusiera a tierra, que es el estado “bajo” o 0. Así, un 1 in resultó en un 0 out, y viceversa.

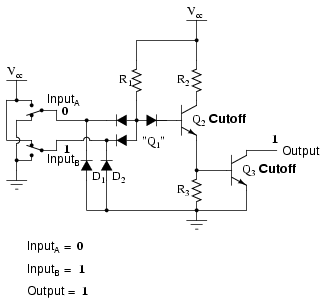

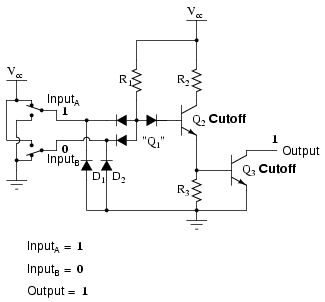

Dado que este circuito tiene tanto parecido con el circuito inversor simple, siendo la única diferencia un segundo terminal de entrada conectado de la misma manera a la base del transistor Q 2, podemos decir que cada una de las entradas tendrá el mismo efecto en la salida. Es decir, si alguna de las entradas está puesta a tierra, el transistor Q 2 se verá forzado a una condición de corte, apagando así Q 3 y flotando la salida (la salida va “alta”). La siguiente serie de ilustraciones muestra esto para tres estados de entrada (00, 01 y 10):

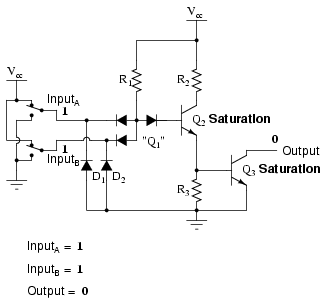

En cualquier caso, donde hay una entrada puesta a tierra (“baja”), se garantiza que la salida sea flotante (“alta”). Por el contrario, la única vez que la salida irá “baja” es si el transistor Q3 se enciende, lo que significa que el transistor Q2 debe estar encendido (saturado), lo que significa que ninguna de las entradas puede estar desviando la corriente R1 lejos de la base de Q2. La única condición que satisfará este requisito es cuando ambas entradas son “altas” (1):

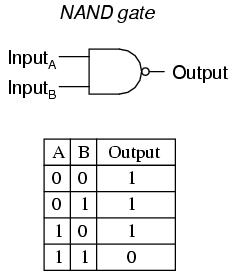

Puerta NAND

Recolectando y tabulando estos resultados en una tabla de verdad, vemos que el patrón coincide con el de la puerta NAND:

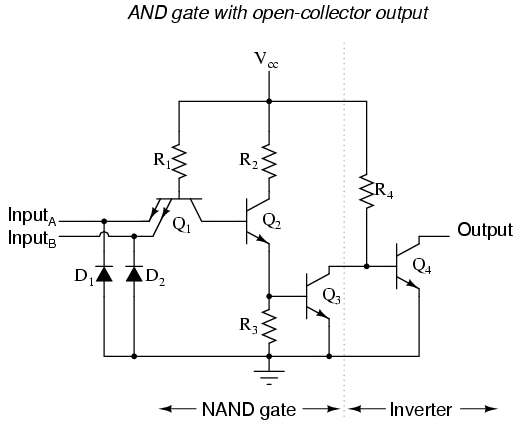

En la sección anterior sobre puertas NAND, este tipo de puerta se creó tomando una puerta AND y aumentando su complejidad al agregar un inversor (NO puerta) a la salida. Sin embargo, cuando examinamos este circuito, vemos que la función NAND es en realidad el modo de operación más simple y natural para este diseño TTL. Para crear una función AND usando circuitos TTL, necesitamos aumentar la complejidad de este circuito agregando una etapa de inversor a la salida, al igual que tuvimos que agregar una etapa de transistor adicional al circuito inversor TTL para convertirlo en un búfer:

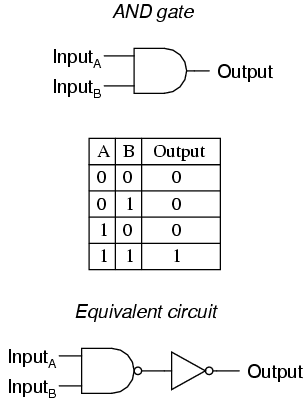

Y Puerta

La tabla de verdad y el circuito de puerta equivalente (una puerta NAND de salida invertida) se muestran aquí:

Por supuesto, tanto los circuitos de puerta NAND como AND pueden diseñarse con etapas de salida de tótem-polo en lugar de colector abierto. Estoy optando por mostrar las versiones de coleccionista abierto en aras de la simplicidad.

Revisar

- Una puerta TTL NAND se puede hacer tomando un circuito inversor TTL y agregando otra entrada.

- Se puede crear una puerta AND agregando una etapa de inversor a la salida del circuito de puerta NAND.