12.3: Registros de cambio: conversión de entrada en paralelo, salida en serie (PISO)

- Page ID

- 154385

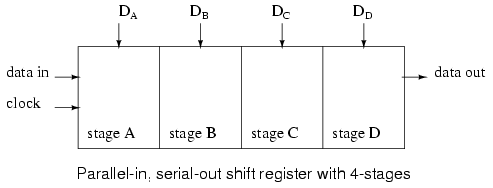

Los registros de desplazamiento de entrada y salida de serie en paralelo hacen todo lo que hacen los registros de desplazamiento de entrada y salida de serie anteriores, además de datos de entrada a todas las etapas simultáneamente. El registro de desplazamiento de entrada y salida de serie en paralelo almacena datos, los desplaza reloj por reloj y los retrasa por el número de etapas por el período del reloj. Además, paralel-in/ serial-out realmente significa que podemos cargar datos en paralelo en todas las etapas antes de que comience cualquier cambio. Esta es una forma de convertir datos de un formato paralelo a un formato serial. Por formato paralelo queremos decir que los bits de datos están presentes simultáneamente en cables individuales, uno por cada bit de datos como se muestra a continuación. Por formato serie queremos decir que los bits de datos se presentan secuencialmente en el tiempo en un solo cable o circuito como en el caso de la “salida de datos” en el diagrama de bloques a continuación.

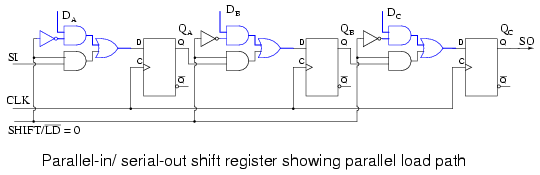

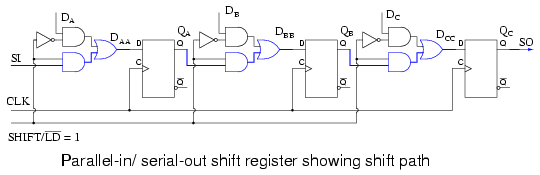

A continuación, analizamos de cerca los detalles internos de un registro de turnos de 3 etapas de entrada y salida de serie en paralelo. Una etapa consiste en un flip-flop tipo D para almacenamiento y un selector AND-OR para determinar si los datos se cargarán en paralelo o desplazarán los datos almacenados hacia la derecha. En general, estos elementos serán replicados para el número de etapas requeridas. Presentamos tres etapas por limitaciones de espacio. Cuatro, ocho o dieciséis bits es normal para piezas reales.

Arriba mostramos la ruta de carga paralela cuando SHIFT/LD' es lógico bajo. Se habilitan las puertas NAND superiores que sirven D A D B D C, pasando datos a las entradas D de tipo D Flip-Flops Q A Q B D C respectivamente. En el siguiente borde positivo del reloj, los datos serán cronometrados de D a Q de los tres FFs. Tres bits de datos se cargarán en Q A Q B D C al mismo tiempo.

El tipo de carga paralela que se acaba de describir, donde las cargas de datos en un pulso de reloj se conoce como carga sincrónica porque la carga de datos se sincroniza con el reloj. Esto debe diferenciarse de la carga asíncrona donde la carga es controlada por los pines preestablecidos y claros de los flip-flops que no requieren el reloj. Solo uno de estos métodos de carga se utiliza dentro de un dispositivo individual, siendo la carga síncrona más común en los dispositivos más nuevos.

La ruta de desplazamiento se muestra arriba cuando SHIFT/LD' es lógico alto. Las puertas Y inferiores de los pares que alimentan la puerta OR están habilitadas dándonos una conexión de registro de turnos de SI a D A, Q A a D B, Q B a D C, Q C a SO. Los pulsos de reloj harán que los datos se desvíen a la derecha a SO en pulsos sucesivos.

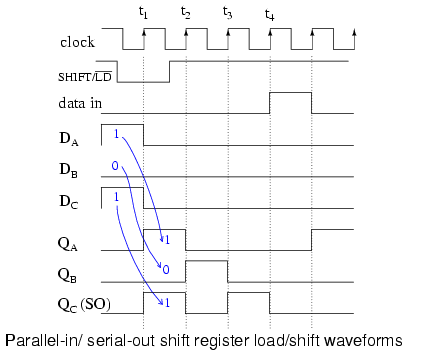

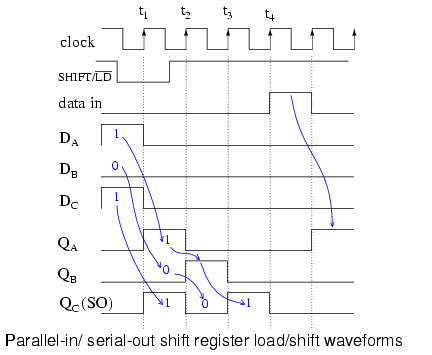

Las formas de onda siguientes muestran tanto la carga paralela de tres bits de datos como el desplazamiento en serie de estos datos. Los datos paralelos en D A D B D C se convierten a datos en serie en SO.

Lo que anteriormente describimos con palabras para carga y desplazamiento en paralelo ahora se establece como formas de onda arriba. Como ejemplo presentamos 101 a las entradas paralelas D AA D BB D CC. A continuación, el SHIFT/LD' va bajo permitiendo la carga de datos en lugar de desplazamiento de datos. Debe estar bajo poco tiempo antes y después del pulso del reloj debido a los requisitos de configuración y retención. Es considerablemente más ancho de lo que tiene que ser. Sin embargo, con lógica sincrónica es conveniente hacerlo amplio. Podríamos haber hecho el activo bajo SHIFT/LD' casi dos relojes de ancho, bajo casi un reloj antes de t 1 y volver alto justo antes de t 3. El factor importante es que necesita ser bajo alrededor del tiempo de reloj t1 para permitir la carga paralela de los datos por el reloj.

Obsérvese que en t 1 los datos 101 en D A D B D C se sincronizan de D a Q de los flip-flops como se muestra en Q A Q B Q C en el tiempo t1. Esta es la carga paralela de los datos sincrónicos con el reloj.

Ahora que los datos están cargados, podemos desplazarlos siempre que SHIFT/LD' sea alto para habilitar el desplazamiento, que es anterior a t 2. En t 2 los datos 0 en Q C se desplazan fuera de SO, que es lo mismo que la forma de onda QC. O se desplaza a otro circuito integrado, o se pierde si no hay nada conectado al SO. Los datos en Q B, a 0 se desplazan a Q C. El 1 en Q A se desplaza a Q B. Con “datos en” a 0, Q A se convierte en 0. Después de t 2, Q A Q B Q C = 010.

Después de t 3, Q A Q B Q C = 001. Este 1, que originalmente estaba presente en Q A después de t 1, ahora está presente en SO y Q C. El último bit de datos se desplaza a un circuito integrado externo si existe. Después de t 4 todos los datos de la carga paralela se han ido. En el reloj t 5 mostramos el desplazamiento de un dato 1 presente en el SI, entrada serial.

¿Por qué proporcionar pines SI y SO en un registro de turnos? Estas conexiones nos permiten poner en cascada etapas del registro de cambios para proporcionar cambiadores grandes que los disponibles en un solo paquete IC (Circuito Integrado). También permiten conexiones en serie hacia y desde otros CI como microprocesadores. Echemos un vistazo más de cerca a los registros de cambios de entrada y salida en paralelo disponibles como circuitos integrados, cortesía de Texas Instruments. Para obtener las hojas de datos completas del dispositivo, siga estos enlaces.

Dispositivos de entrada y salida en serie en paralelo

- SN74ALS166 registro de desplazamiento de 8 bits en paralelo y salida en serie, carga síncrona - ejemplo

- SN74ALS165 registro de desplazamiento de 8 bits en paralelo y salida en serie, carga asíncrona - ejemplo

- CD4014B registro de desplazamiento de 8 bits en paralelo y salida en serie, carga síncrona - ejemplo

- SN74LS647 registro de desplazamiento de 16 bits en paralelo y salida en serie, carga síncrona - ejemplo

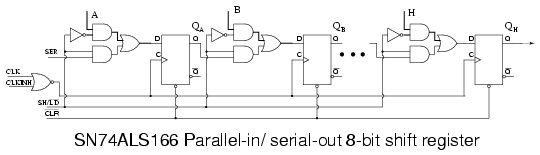

El SN74ALS166 que se muestra arriba es la coincidencia más cercana de una parte real con las figuras anteriores de la palanca de cambios de salida de paralelo/serie. Tomemos nota de los cambios menores a nuestra figura anterior. En primer lugar, hay 8 etapas. Sólo mostramos tres. Todas las 8 etapas se muestran en la hoja de datos disponible en el enlace anterior. El fabricante etiqueta las entradas de datos A, B, C, y así sucesivamente a H. El control SHIFT/LOAD se llama SH/LD'. Se abrevia de nuestra terminología anterior, pero funciona de la misma manera: carga paralela si es baja, cambio si es alta. La entrada de desplazamiento (entrada de datos en serie) es SER en el ALS166 en lugar de SI. El reloj CLK es controlado por una señal de inhibición, CLKINH. Si CLKINH es alto, el reloj se inhibe o se desactiva. De lo contrario, esta “parte real” es la misma que la que hemos visto en detalle.

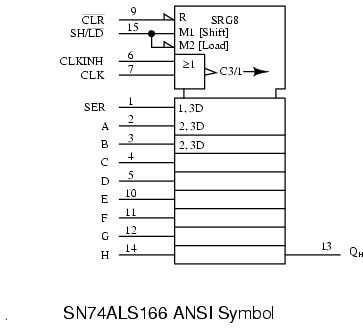

Arriba está el símbolo ANSI (American National Standards Institute) para el SN74ALS166 tal como se proporciona en la hoja de datos. Una vez que sabemos cómo opera la pieza, es conveniente ocultar los detalles dentro de un símbolo. Hay muchas formas generales de símbolos. La ventaja del símbolo ANSI es que las etiquetas proporcionan pistas sobre cómo opera la pieza.

El bloque grande con muescas en la parte superior del '74ASL166 es la sección de control del símbolo ANSI. Hay un reset inculpado por R. Hay tres señales de control: M1 (Shift), M2 (Load) y C3/1 (flecha) (reloj inhibido). El reloj tiene dos funciones. Primero, C3 para desplazar datos paralelos donde aparezca un prefijo de 3. Segundo, cada vez que se afirma M1, como lo indica el 1 de C3/1 (flecha), los datos se desplazan como lo indica la flecha que apunta a la derecha. La slash (/) es un separador entre estas dos funciones. Las etapas de 8 turnos, como indica el título SRG8, son identificadas por las entradas externas A, B, C, a H. El 2 interno, 3D indica que los datos, D, están controlados por M2 [Carga] y C3 reloj. En este caso, podemos concluir que los datos paralelos se cargan sincrónicamente con el reloj C3. La etapa superior en A es un bloque más ancho que los otros para acomodar el SER de entrada. La leyenda 1, 3D implica que SER está controlado por M1 [Shift] y C3 reloj. Por lo tanto, esperamos registrar los datos en SER cuando se desplaza en lugar de la carga paralela.

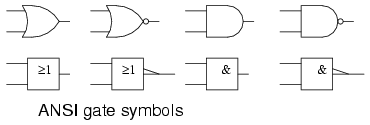

Los símbolos rectangulares de puerta básica ANSI/IEEE se proporcionan anteriormente para compararlos con los símbolos de forma más familiares para que podamos descifrar el significado de la simbología asociada con los pines CLKIN H y CLK en el ANSI SN anterior Símbolo 74ALS166. El CLK y el CLKINH alimentan una puerta OR en el símbolo SN74ALS166 ANSI. O se indica con => en el símbolo de inserción rectangular. El triángulo largo en la salida indica un reloj. Si hubiera una burbuja con la flecha esto habría indicado desplazamiento en el borde negativo del reloj (alto a bajo). Como no hay burbuja con la flecha del reloj, el registro cambia en el borde del reloj positivo (transición baja a alta). La flecha larga, después de la leyenda C3/1 apuntando a la derecha indica desplazamiento a la derecha, que está abajo del símbolo.

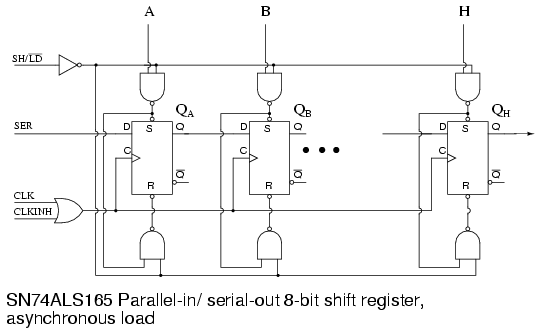

Parte de la lógica interna del registro de desplazamiento de carga asíncrono de entrada y salida en serie SN74ALS165 se reproduce a partir de la hoja de datos anterior. Consulte el enlace al inicio de esta sección el para ver el diagrama completo. No hemos mirado la carga asincrónica de datos hasta este punto. En primer lugar, la carga se logra mediante la aplicación de señales apropiadas a las entradas Set (preset) y Reset (clear) de los Flip-Flops. Las compuertas NAND superiores alimentan los pines Set de los FFs y también caen en cascada en la puerta NAND inferior alimentando los pines de reinicio de los FFs. La puerta NAND inferior invierte la señal al pasar del pin Set al pin Reset.

Primero, SH/LD' debe tirarse bajo para habilitar las puertas NAND superior e inferior. Si SH/LD' estuviera en un nivel lógico alto en su lugar, el inversor que alimenta una lógica baja a todas las puertas NAND forzaría una salida alta, liberando el conjunto “bajo activo” y Restablecer pines de todos los FFs. No habría posibilidad de cargar los FFs.

Con SH/LD' mantenido bajo, podemos alimentar, por ejemplo, un dato 1 a la entrada paralela A, que se invierte a un cero en la salida de la puerta NAND superior, configurando FF Q A a 1. El 0 en el pin Set se alimenta a la puerta NAND inferior donde se invierte a un 1, liberando el pin Reset de Q A. Así, un dato A=1 establece Q A =1. Dado que nada de esto requirió el reloj, la carga es asíncrona con respecto al reloj. Usamos un registro de desplazamiento de carga asíncrono si no podemos esperar a que un reloj cargue datos en paralelo, o si es inconveniente generar un solo pulso de reloj.

La única diferencia en la alimentación de un dato 0 a la entrada paralela A es que se invierte a un 1 fuera de la puerta superior liberando Set. Este 1 en Set se invierte a un 0 en la puerta inferior, tirando de Reset to a Low, que restablece Q A =0.

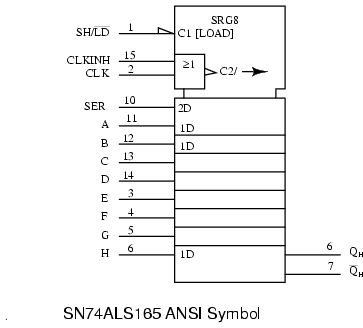

El símbolo ANSI para el SN74ALS166 anterior tiene dos controles internos C1 [LOAD] y C2 reloj de la función OR de (CLKINH, CLK). SRG8 dice palanca de cambios de 8 etapas. La flecha después de C2 indica desplazamiento hacia la derecha o hacia abajo. La entrada SER es una función del reloj como lo indica la etiqueta interna 2D. Las entradas de datos paralelos A, B, C a H son una función de C1 [CARGA], indicada por la etiqueta interna 1D. C1 se afirma cuando SH/ld' =0 debido al inversor de media flecha en la entrada. Compare esto con el control de las entradas de datos paralelos por el reloj de la anterior ANSI SN75ALS166 síncrona. Tenga en cuenta las diferencias en las etiquetas ANSI Data.

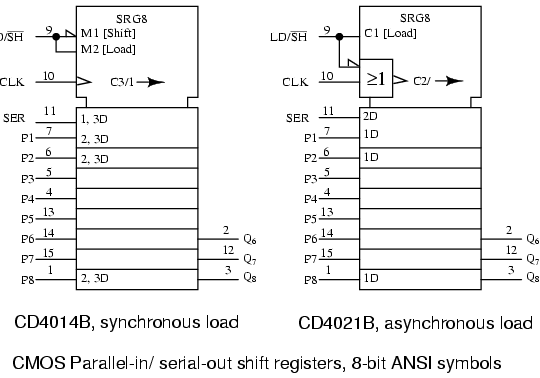

En el CD4014B anterior, M1 se afirma cuando LD/SH'=0. M2 se afirma cuando LD/SH'=1. El reloj C3/1 se utiliza para cargar datos en paralelo a 2, 3D cuando M2 está activo como lo indican las etiquetas de prefijo 2,3. Se entiende que los pines P3 a P7 tienen las etiquetas internas de prefijo 2,3 smae como P2 y P8. En SER, el prefijo 1,3D implica que M1 y el reloj C3 son necesarios para ingresar datos en serie. El desplazamiento a la derecha tiene lugar cuando M1 activo es como lo indica la flecha 1 en C3/1.

El CD4021B es una parte similar a excepción de la carga asíncrona paralela de datos como implica la falta de cualquier prefijo 2 en la etiqueta de datos 1D para los pines P1, P2, a P8. Por supuesto, el prefijo 2 en la etiqueta 2D en la entrada SER dice que los datos se registran en este pin. El recuadro de puerta OR muestra que el reloj está controlado por LD/SH'.

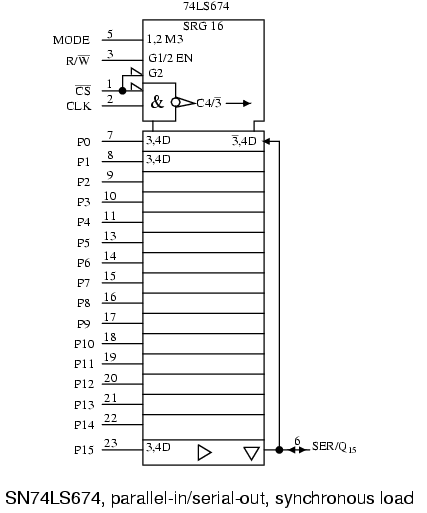

La etiqueta interna SRG 16 anterior SN74LS674 indica un registro de desplazamiento de 16 bits. La entrada MODE a la sección de control en la parte superior del símbolo está etiquetada con 1,2 M3. Interno M3 es una función de entrada MODE y G1 y G2 como lo indica el 1,2 anterior M3. La etiqueta base G indica una función AND de cualquiera de tales entradas G. La entrada R/W' está etiquetada internamente G1/2 EN. Esta es una habilitación EN (controlada por G1 Y G2) para dispositivos triestatales utilizados en otra parte del símbolo. Observamos que CS' on (pin 1) es interno G2. Chip select CS' también es Y ed con la entrada CLK para dar reloj interno C4. La burbuja dentro de la flecha del reloj indica que la actividad está en el borde negativo (transición alta a baja) del reloj. El slash (/) es un separador que implica dos funciones para el reloj. Antes de la barra, C4 indica el control de cualquier cosa con un prefijo de 4. Después de la baraja, el 3' (flecha) indica desplazamiento. El 3' de C4/3' implica desplazamiento cuando M3 se desafirma (MODO=0). La flecha larga indica desplazamiento a la derecha (abajo).

Bajando por debajo de la sección de control a la sección de datos, tenemos entradas externas P0-P15, pines (7-11, 13-23). El prefijo 3,4 de la etiqueta interna 3,4D indica que M3 y el reloj C4 controlan la carga de datos paralelos. La D significa Datos. Se supone que esta etiqueta se aplica a todas las entradas paralelas, aunque no explícitamente escrita. Localice la etiqueta 3',4D a la derecha de la etapa P0 (pin7). El complementado- 3 indica que M3 = MODO=0 entradas (desplazamientos) SER/Q 15 (pin5) en tiempo de reloj, (4 de 3',4D) correspondientes al reloj C4 . En otras palabras, con MODO=0, cambiamos los datos a Q 0 desde la entrada serial (pin 6). Todas las demás etapas cambian a la derecha (abajo) en el tiempo del reloj.

Al pasar a la parte inferior del símbolo, el triángulo que apunta a la derecha indica un búfer entre Q y el pin de salida. El Triángulo apuntando hacia abajo indica un dispositivo de tres estados. Anteriormente afirmamos que el triestado está controlado por enable EN, que en realidad es G1 Y G2 desde la sección de control. Si R/W=0, el tri-estado está deshabilitado, y podemos cambiar los datos a Q 0 a través de SER (pin 6), un detalle que omitimos anteriormente. En realidad necesitamos MODO=0, R/W'=0, CS'=0

La lógica interna del SN74LS674 y una tabla que resume el funcionamiento de las señales de control está disponible en el enlace en la lista de viñetas, parte superior de la sección.

Si R/W'=1, el triestado está habilitado, Q 15 desplaza hacia fuera SER/Q 15 (pin 6) y recircula a la etapa Q 0 a través del cable derecho a 3',4D . Hemos asumido que CS' era bajo dándonos reloj C4/3' y G2 a EN capaz el tri-estado.

Aplicaciones prácticas

Una aplicación de un registro de desplazamiento de entrada y salida de serie en paralelo es leer datos en un microprocesador.

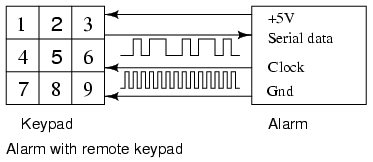

La Alarma de arriba es controlada por un teclado remoto. La caja de alarma suministra +5V y tierra al teclado remoto para alimentarlo. La alarma lee el teclado remoto cada pocas decenas de milisegundos enviando relojes de turno al teclado que devuelve datos en serie que muestran el estado de las teclas a través de un registro de desplazamiento de entrada y salida de serie en paralelo. Así, leemos nueve interruptores de llave con cuatro cables. ¿Cuántos cables se necesitarían si tuviéramos que ejecutar un circuito para cada una de las nueve llaves?

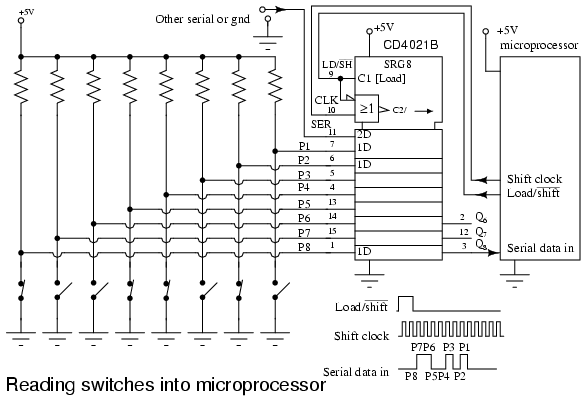

Una aplicación práctica de un registro de desplazamiento de entrada y salida de serie en paralelo es leer muchos cierres de interruptores en un microprocesador en solo unos pocos pines. Algunos microprocesadores de gama baja solo tienen pines de 6 E/S (Entrada/Salida) disponibles en un paquete de 8 pines. O bien, es posible que hayamos usado la mayoría de los pines en un paquete de 84 pines. Es posible que queramos reducir la cantidad de cables que circulan alrededor de una placa de circuito, una máquina, un vehículo o un edificio. Esto aumentará la confiabilidad de nuestro sistema. Se ha reportado que los fabricantes que han reducido el número de cables en un automóvil producen un producto más confiable. En cualquier caso, solo se requieren tres pines de microprocesador para leer en 8 bits de datos de los conmutadores en la figura anterior.

Hemos elegido un dispositivo de carga asíncrono, el CD4021B porque es más fácil controlar la carga de datos sin tener que generar un solo reloj de carga paralela. Las entradas de datos en paralelo del registro de desplazamiento se elevan hasta +5V con una resistencia en cada entrada. Si todos los interruptores están abiertos, todos los 1 s se cargarán en el registro de cambios cuando el microprocesador mueva la línea LD/SH' de bajo a alto, luego hacia atrás bajo en anticipación del cambio. Cualquier cierre de conmutador aplicará 0 s lógicos a las entradas paralelas correspondientes. El patrón de datos en P1-P7 será cargado en paralelo por el LD/SH'=1 generado por el software del microprocesador.

El microprocesador genera pulsos de desplazamiento y lee un bit de datos para cada uno de los 8 bits. Este proceso se puede realizar totalmente con software, o los microprocesadores más grandes pueden tener una o más interfaces serie para hacer la tarea más rápidamente con el hardware. Con LD/SH'=0, el microprocesador genera una transición de 0 a 1 en la línea de reloj Shift, luego lee un bit de datos en los datos Serial en línea. Esto se repite para todos los 8 bits.

La línea SER del registro de desplazamiento puede ser accionada por otro circuito CD4021B idéntico si es necesario leer más contactos del interruptor. En cuyo caso, el microprocesador genera pulsos de 16 turnos. Lo más probable es que esté impulsado por algo más compatible con este formato de datos serie, por ejemplo, un convertidor analógico a digital, un sensor de temperatura, un escáner de teclado, una memoria serial de solo lectura. En cuanto a los cierres de los interruptores, pueden ser interruptores de límite en el carro de una máquina, un sensor de sobretemperatura, un interruptor de láminas magnético, un interruptor de puerta o ventana, un interruptor de presión de aire o agua, o un interruptor óptico de estado sólido.