2.9: Estudio de caso- Diseño de Amplificador Lineal de Banda Estrecha

- Page ID

- 86117

\( \newcommand{\vecs}[1]{\overset { \scriptstyle \rightharpoonup} {\mathbf{#1}} } \)

\( \newcommand{\vecd}[1]{\overset{-\!-\!\rightharpoonup}{\vphantom{a}\smash {#1}}} \)

\( \newcommand{\id}{\mathrm{id}}\) \( \newcommand{\Span}{\mathrm{span}}\)

( \newcommand{\kernel}{\mathrm{null}\,}\) \( \newcommand{\range}{\mathrm{range}\,}\)

\( \newcommand{\RealPart}{\mathrm{Re}}\) \( \newcommand{\ImaginaryPart}{\mathrm{Im}}\)

\( \newcommand{\Argument}{\mathrm{Arg}}\) \( \newcommand{\norm}[1]{\| #1 \|}\)

\( \newcommand{\inner}[2]{\langle #1, #2 \rangle}\)

\( \newcommand{\Span}{\mathrm{span}}\)

\( \newcommand{\id}{\mathrm{id}}\)

\( \newcommand{\Span}{\mathrm{span}}\)

\( \newcommand{\kernel}{\mathrm{null}\,}\)

\( \newcommand{\range}{\mathrm{range}\,}\)

\( \newcommand{\RealPart}{\mathrm{Re}}\)

\( \newcommand{\ImaginaryPart}{\mathrm{Im}}\)

\( \newcommand{\Argument}{\mathrm{Arg}}\)

\( \newcommand{\norm}[1]{\| #1 \|}\)

\( \newcommand{\inner}[2]{\langle #1, #2 \rangle}\)

\( \newcommand{\Span}{\mathrm{span}}\) \( \newcommand{\AA}{\unicode[.8,0]{x212B}}\)

\( \newcommand{\vectorA}[1]{\vec{#1}} % arrow\)

\( \newcommand{\vectorAt}[1]{\vec{\text{#1}}} % arrow\)

\( \newcommand{\vectorB}[1]{\overset { \scriptstyle \rightharpoonup} {\mathbf{#1}} } \)

\( \newcommand{\vectorC}[1]{\textbf{#1}} \)

\( \newcommand{\vectorD}[1]{\overrightarrow{#1}} \)

\( \newcommand{\vectorDt}[1]{\overrightarrow{\text{#1}}} \)

\( \newcommand{\vectE}[1]{\overset{-\!-\!\rightharpoonup}{\vphantom{a}\smash{\mathbf {#1}}}} \)

\( \newcommand{\vecs}[1]{\overset { \scriptstyle \rightharpoonup} {\mathbf{#1}} } \)

\( \newcommand{\vecd}[1]{\overset{-\!-\!\rightharpoonup}{\vphantom{a}\smash {#1}}} \)

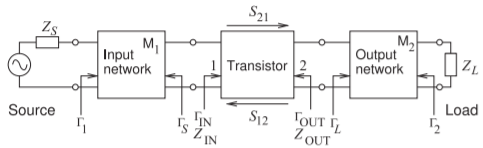

El procedimiento de diseño para amplificadores lineales está bien desarrollado y la estrategia forma la base para todo el diseño de amplificadores. Un amplificador tiene tres componentes principales: una red de coincidencia de entrada, un dispositivo activo y una red de coincidencia de salida (consulte la Figura\(\PageIndex{1}\)). Hay una serie de opciones de diseño a realizar y éstas se ilustrarán considerando el diseño de un amplificador para ganancia máxima usando el transistor discreto PheMT examinado previamente (ver Tabla 2.3.1). Las especificaciones de diseño son

Figura\(\PageIndex{1}\): Amplificador lineal que comprende redes de adaptación de entrada y salida y un dispositivo activo en una configuración específica que forma un puerto de dos.

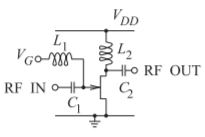

Figura\(\PageIndex{2}\): Configuración de polarización para amplificador PhemT. \(L_{1}\)y\(L_{2}\) son estranguladores de RF y lo suficientemente grandes como para bloquear RF. \(C_{1}\)y\(C_{2}\) son condensadores de bloqueo de CC que bloquean CC pero permiten que la RF pase con impedancia insignificante.

\[\begin{array}{ll}{\text{Gain:}}&{\text{maximum gain at }8\text{ GHz}} \\ {\text{Topology:}}&{\text{three two-ports (input and output matching}}\\{}&{\text{networks, and the active device)}}\\{\text{Stability:}}&{\text{broadband stability}}\\{\text{Bandwidth:}}&{\text{maximum that can be achieved using two-}}\\{}&{\text{element matching networks}}\\{\text{Source impedance:}}&{Z_{S}=50\:\Omega}\\{\text{Load impedance:}}&{Z_{L}=50\:\Omega}\end{array}\nonumber \]

2.9.1 Topología de circuito de polarización

El primer paso de diseño es elegir una configuración de polarización, y esto está directamente relacionado con la oscilación de voltaje de salida soportada. Se\(\PageIndex{2}\) utilizará la configuración polarizada inductivamente en la Figura. Aquí\(L_{1}\) y\(L_{2}\) hay choques de RF y lo suficientemente grandes como para bloquear RF. \(C_{1}\)y\(C_{2}\) son condensadores de bloqueo de CC que bloquean CC pero permiten que la RF pase con impedancia insignificante. La red de coincidencia de entrada está conectada al terminal RF IN y la red de coincidencia de salida está conectada al terminal RF OUT. \(V_{DD}\)es el voltaje de suministro y\(V_{G}\) es el voltaje de compuerta de CC generalmente proporcionado por un circuito integrado analógico disponible junto con la mayoría de los diseños de RF. Un objetivo de diseño adicional es absorber el circuito de polarización en las redes coincidentes.

2.9.2 Consideraciones de estabilidad

No es suficiente considerar una sola frecuencia en el diseño, ya que la estabilidad debe garantizarse a frecuencias bajas y altas. El factor de estabilidad del dispositivo activo se dio en la Tabla 2.6.2. Esto indica que el dispositivo es incondicionalmente estable desde\(11\text{ GHz}\) y\(5\)\(22\) hacia\(26\text{ GHz}\). En el extremo de alta frecuencia, la ganancia del dispositivo se reduce rápidamente al aumentar la frecuencia a medida que los parásitos capacitivos comienzan a dominar la transmisión a través del dispositivo. Por lo tanto, es razonable suponer que el dispositivo es incondicionalmente estable arriba\(22\text{ GHz}\).

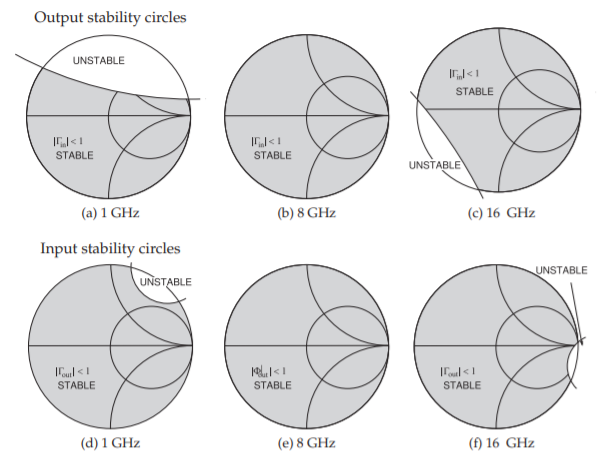

El diseño casi siempre comienza con la red de coincidencia de salida. El primer paso de diseño es elegir una red coincidente que proporcione las impedancias adecuadas para garantizar la estabilidad por debajo\(5\text{ GHz}\) y por encima\(11\text{ GHz}\). Para ello se deben considerar los círculos de estabilidad, ya que el dispositivo sólo es condicionalmente estable a estas frecuencias. El centro y el radio de los círculos de estabilidad de entrada y salida se enumeran en la Tabla 2.6.1. Estos se trazan en la Figura\(\PageIndex{3}\) para frecuencias seleccionadas.

2.9.3 Diseño de red de coincidencia de salida

El círculo de estabilidad de salida en\(1\text{ GHz}\) (ver Figura\(\PageIndex{3}\) (a)) indica que para una amplificación estable de baja frecuencia, la red de coincidencia de salida, como se ve desde el transistor, podría parecer un cortocircuito, una carga coincidente o un condensador a bajas frecuencias. Figura\(\PageIndex{3}\) (c), el círculo de estabilidad de salida en

Figura\(\PageIndex{3}\): Círculos de estabilidad de entrada y salida en los planos de coeficientes de reflexión complejos para\(|S_{11}| < 1\) y\(|S_{22}| < 1\).

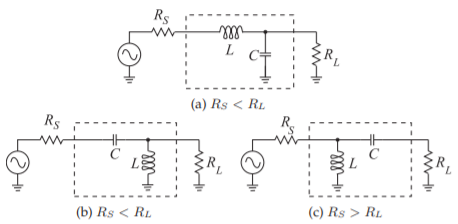

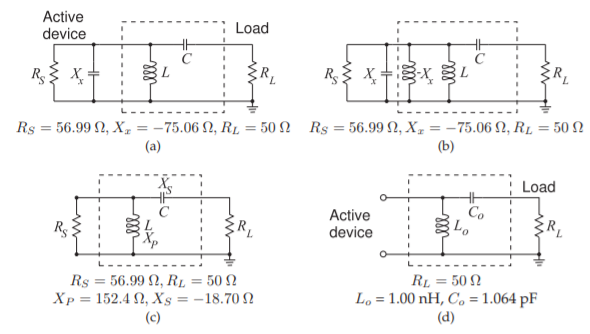

Figura\(\PageIndex{4}\): Los candidatos de red de coincidencia de salida requeridos para la estabilidad fuera de banda. El dispositivo activo está a la izquierda.

\(16\text{ GHz}\), indica que para una amplificación estable de alta frecuencia, la red de coincidencia de salida, como se ve desde el transistor, podría parecer un circuito abierto o una carga coincidente a altas frecuencias. Como era de esperar, el círculo de estabilidad de salida en\(8\text{ GHz}\)\(\PageIndex{3}\) (ver Figura (b)) indica estabilidad incondicional. Al examinar las redes coincidentes de dos elementos en la Figura 6-7 de [2], hay tres redes de coincidencia de salida candidatas que se muestran en la Figura\(\PageIndex{4}\).

De la Tabla 2.3.1, los\(S\) parámetros del dispositivo en\(8\text{ GHz}\) son los siguientes:

\[\begin{array}{ll}{S_{11}=0.486\angle 140.4^{\circ}}&{S_{21}=3.784\angle 11.2^{\circ}} \\{S_{12}=0.057\angle 6.4^{\circ}}&{S_{22}=0.340\angle -99.1^{\circ}}\end{array}\nonumber \]

Para comenzar, ignora\(S_{12}\) para que\(\Gamma_{\text{OUT}} = S_{22} = 0.340\angle −99.1\). Aquí hay pocas opciones ya que\(\Gamma_{\text{OUT}}\) depende de la red de coincidencia de entrada que aún no se ha diseñado. Habría sido posible comenzar con la red de coincidencia de entrada y hacer esta aproximación para\(\Gamma_{\text{IN}}\). Sin embargo, la experiencia es que el error introducido al comenzar con la red de coincidencia de salida es menor. Una vez que se ha diseñado la red de coincidencia de salida, se\(\Gamma_{\text{IN}}\) puede calcular sin aproximación. Un diseño minucioso completaría la primera pasada del diseño y luego haría una pasada más sin la aproximación que ignora\(S_{12}\). Ahora, con\(\Gamma_{\text{OUT}} = S_{22}\), la impedancia de salida del dispositivo activo es

\[\begin{align}Z_{\text{OUT}}&=Z_{0}\frac{1+\Gamma_{\text{OUT}}}{1-\Gamma_{\text{OUT}}}=Z_{0}\frac{1+S_{22}}{1-S_{22}}\nonumber \\ &=(50\:\Omega )\frac{1+(0.340\angle -99.1^{\circ})}{1-(0.340\angle -99.1^{\circ})}=(50\:\Omega)\frac{1+(-0.053774-\jmath 0.335721)}{1-(-0.053774 - \jmath 0.335721)}\nonumber \\ \label{eq:1}&=36.153-\jmath 27.447\:\Omega\end{align} \]

o\(Y_{\text{OUT}} = 1/Z_{\text{OUT}} = 0.017547 + \jmath 0.013322\text{ S}\). La salida del dispositivo activo parece una\(56.99\:\Omega\) resistencia en paralelo con un condensador con una reactancia de\(−75.064\:\Omega\). Entonces, tomando en cuenta los objetivos de sesgo y las redes de coincidencia de salida disponibles en la Figura\(\PageIndex{4}\), se utilizará la topología de red coincidente de la Figura\(\PageIndex{4}\) (c) donde la fuente en la red coincidente es el dispositivo activo. Entonces, el problema de red de coincidencia de salida es como se muestra en la Figura\(\PageIndex{5}\). Esta elección permite que el inductor se utilice para aplicar sesgo.

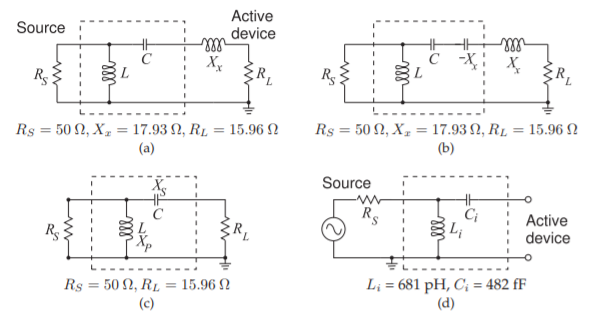

El problema completo de coincidencia de salida se muestra en la Figura\(\PageIndex{5}\) (a). En parte, se eligió la configuración paralela de la impedancia de salida del dispositivo activo, ya que esta se acerca más a la realidad ya que hay una capacitancia en la salida del transistor. La resonancia, como se muestra en la Figura\(\PageIndex{5}\) (b), se utilizará para cancelar el efecto de la capacitancia activa del dispositivo, de manera que el problema de coincidencia se reduzca al mostrado en la Figura\(\PageIndex{5}\) (c). Utilizando el procedimiento descrito en la Sección 6.4.2 de [2],

\[\label{eq:2}|Q_{S}|=|Q_{P}|=\sqrt{\frac{R_{S}}{R_{L}}-1}=\sqrt{\frac{56.99}{50}-1}=0.3739 \]

\[\label{eq:3}Q_{S}=\left|\frac{X_{S}}{R_{L}}\right| = \left|\frac{X_{S}}{50\:\Omega}\right|=0.3739\text{ and }Q_{P}=\left|\frac{R_{S}}{X_{P}}\right|=\left|\frac{56.99\:\Omega}{X_{P}}\right|=0.3739 \]

entonces

\[\label{eq:4}X_{S}=-18.70\:\Omega\quad\text{and}\quad X_{P}=152.4\:\Omega \]

Ahora\(X_{x} = −75.064\:\Omega\), así se\(75.064\:\Omega\) debe agregar a\(X_{P}\) en paralelo, y la reactancia de\(L_{o}\) es\(50.29\:\Omega\), así (at\(8\text{ GHz}\))

\[\label{eq:5}L_{o}=1.00\text{ nH}\quad\text{and}\quad C_{o}=1.064\text{ pF} \]

El diseño final de la red de coincidencia de salida se muestra en la Figura\(\PageIndex{5}\) (d).

Figura\(\PageIndex{5}\): Pasos en el diseño de la red de adaptación de salida: (a) el dispositivo activo se presenta como una resistencia en paralelo con una reactancia capacitiva a la red de adaptación de salida; (b) con inductor para resonar la reactancia activa del dispositivo; (c) problema de red de adaptación simplificada; y (d) salida final diseño de red coincidente.

Figura\(\PageIndex{6}\): Se requieren candidatos de red coincidentes de entrada para la estabilidad fuera de banda. El dispositivo activo está a la derecha.)

2.9.4 Diseño de Red de Coincidencia de Entrada

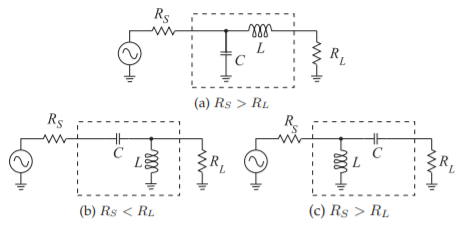

El círculo de estabilidad de entrada en\(1\text{ GHz}\)\(\PageIndex{3}\) (Figura (d)) indica que at\(1\text{ GHz}\), la red de coincidencia de entrada, como se ve desde el transistor, podría parecer un cortocircuito, una carga coincidente o un condensador a bajas frecuencias. La figura\(\PageIndex{3}\) (f), el círculo de estabilidad de entrada en\(16\text{ GHz}\), indica que la red de coincidencia de entrada, como se ve desde el transistor, podría parecer un cortocircuito o una carga coincidente a altas frecuencias. Al examinar las redes coincidentes de dos elementos en la Figura 6-7 de [2], hay tres redes de coincidencia de entrada candidatas como se muestra en la Figura\(\PageIndex{6}\).

El coeficiente de reflexión que busca en la red de coincidencia de salida desde el dispositivo activo se\(\Gamma_{L} = S_{22}^{\ast} = 0.340\angle 99.1^{\circ}\) debe a la decisión de diseño a ignorar\(S_{12}\) para la red de coincidencia de salida. Ahora que la salida coincidente

Figura\(\PageIndex{7}\): Pasos en el diseño de la red de adaptación de entrada: (a) el dispositivo activo se presenta como una resistencia en serie con una reactancia inductiva a la red de adaptación de entrada; (b) con un condensador para resonar la reactancia del dispositivo activo; (c) problema de red de adaptación simplificada; y (d) final diseño de red coincidente de salida.

red ha sido diseñada, el parámetro de retroalimentación ya no necesita ser ignorado. Entonces

\[\begin{align}\label{eq:6}\Gamma_{\text{IN}}&=S_{11}+\frac{S_{12}S_{21}\Gamma_{L}}{1-S_{22}\Gamma_{L}} \\ \label{eq:7}&=(0.486\angle 140.4^{\circ})+\frac{(0.057\angle 6.4^{\circ})(3.784\angle 11.2^{\circ})(0.340\angle 99.1^{\circ})}{1− (0.340\angle −99.1^{\circ})(0.340\angle 99.1^{\circ})} \\ \label{eq:8}&=-0.4117+\jmath 0.3839\end{align} \]

Es decir,\(Z_{\text{IN}} = 15.959 +\jmath 17.935\:\Omega\). Entonces tomando en cuenta los objetivos de sesgo y las redes de coincidencia de salida mostradas en la Figura\(\PageIndex{6}\), se utilizará la topología de red coincidente de la Figura\(\PageIndex{6}\) (c) (donde la carga es el dispositivo activo). El problema de la red de coincidencia de entrada es como se muestra en la Figura\(\PageIndex{7}\) (c). (El sesgo no se puede incorporar a esta red coincidente). Ahora

\[\begin{align}\label{eq:9}|Q_{S}|&=|Q_{P}|=\sqrt{\frac{R_{S}}{R_{L}}-1}=\sqrt{\frac{50}{15.959}-1}=1.4605 \\ \label{eq:10}Q_{S}&=\left|\frac{X_{S}}{R_{L}}\right|=\left|\frac{X_{S}}{15.959\:\Omega}\right|=1.4605\quad\text{and}\quad Q_{P}=\left|\frac{R_{S}}{X_{P}}\right|=\left|\frac{50\:\Omega}{X_{P}}\right|=1.4605\end{align} \]

Entonces

\[\label{eq:11}X_{S}=-23.31\:\Omega\quad\text{and}\quad X_{P}=34.23\:\Omega \]

Dado que\(X_{x} = 17.935\:\Omega\), se\(−17.935\:\Omega\) debe agregar a\(X_{S}\), y la reactancia de\(C_{i}\) es\(41.24\:\Omega\), por lo tanto (at\(8\text{ GHz}\)),

\[\label{eq:12}L_{i}=681\text{ pH}\quad\text{and}\quad C_{i}=482\text{ fF} \]

El diseño final de la red de coincidencia de entrada se muestra en la Figura\(\PageIndex{5}\) (d).

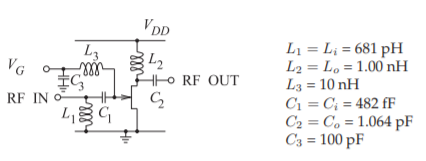

Figura\(\PageIndex{8}\): Esquema final del amplificador.

2.9.5 Diseño de Red Bias

El esquema final del diseño del amplificador lineal se muestra en la Figura\(\PageIndex{8}\). La red de coincidencia de salida\(C_{2}\),\(L_{2}\) y, permitió que el inductor de polarización sea reemplazado por\(L_{2}\). Entonces, el circuito de polarización de salida se absorbe en la red de coincidencia de salida. Un resultado similar no se obtiene con la red de coincidencia de entrada,\(L_{1}\) y\(C_{1}\). Todavía se requiere una red de polarización de puerta separada. \(L_{3}\)debe tener un valor lo suficientemente grande como para que actúe como un estrangulador de RF. Un valor de\(10\text{ nH}\) proporciona una reactancia de aproximadamente\(500\:\Omega\) at\(8\text{ GHz}\). El valor de\(C_{3} = 100\text{ pF}\) se elige lo suficientemente grande como para proporcionar un cortocircuito de RF y estabilizar la polarización de CC,\(V_{G}\). Este es un circuito sorprendentemente simple que proporciona ganancia máxima en\(8\text{ GHz}\), asegura estabilidad fuera de banda y proporciona polarización de CC. Otra iteración de diseño con una red de coincidencia de entrada más sofisticada puede permitir que se elimine el inductor\(L_{3}\) de polarización separado. Tal como está, el circuito de polarización de la puerta asegura aún más la estabilidad a bajas frecuencias, ya que entonces la puerta tiende a cortocircuitarse. El amplificador tiene una ganancia calculada del transductor de\(13.2\text{ dB}\), la cual puede compararse con las ganancias reportadas en la Tabla 2.3.3, donde las métricas de ganancia se determinaron con\(S_{12}\) ignoradas.

También es posible el diseño de amplificador lineal para una ganancia específica. Ahora los errores que implica ignorar\(S_{12}\) durante el proceso de diseño son significativos y se requiere un tratamiento bilateral completo. Este enfoque de diseño se describe en las referencias [11, 27, 28].