3.8: Amplificadores y RFIC

- Page ID

- 86065

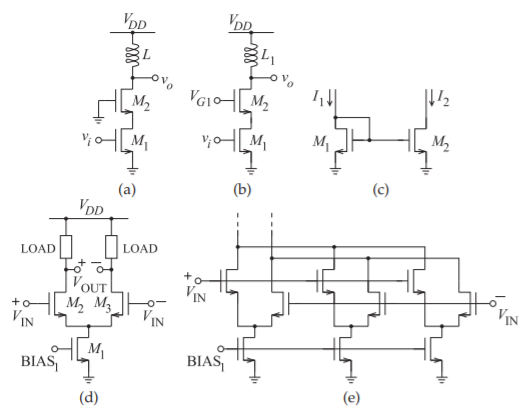

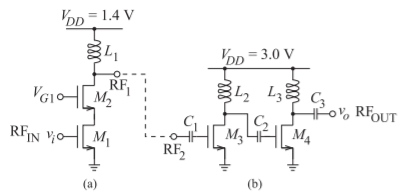

Los RFIC de silicio explotan la integración de alta densidad posible con los transistores MOSFET de silicio. Estos transistores pueden fabricarse con altos niveles de repetibilidad para que los transistores en diseños diferenciales puedan coincidir estrechamente. Además, la compatibilidad inherente con los circuitos digitales permite el control digital de los circuitos de RF. En lo que respecta a los amplificadores, existen algunos circuitos básicos de uso común que utilizan MOSFET complementarios (NMO y PMO), es decir, transistores CMOS. A lo largo de este capítulo se han presentado amplificadores diferenciales MOSFET. Otros circuitos CMOS comunes se muestran en la Figura\(\PageIndex{2}\). Los transistores en todos los circuitos aquí descritos operan en la región de saturación.

Un amplificador cascode se muestra en la Figura\(\PageIndex{2}\) (a). Hay dos FET, con el FET superior actuando como la carga de drenaje del FET inferior. La puerta del FET superior se mantiene a tierra, por lo que el voltaje en la fuente del FET superior (y el drenaje del FET inferior) se mantiene a un voltaje casi constante. Así, el FET superior presenta una carga de baja resistencia al FET inferior. La ganancia de voltaje del FET inferior es baja, y esto reduce la capacitancia del efecto Miller, que es la capacitancia de entrada efectiva (siendo la capacitancia puerta-drenaje multiplicada por la ganancia de voltaje del transistor). La topología cascode aumenta el ancho de banda del circuito. La ganancia de corriente, y por lo tanto la ganancia de potencia, todavía se realiza por el transistor inferior. La ganancia de voltaje del circuito depende de la resistencia presentada al drenaje del transistor superior.

Un amplificador cascode ganancia variable se muestra en la Figura\(\PageIndex{2}\) (b). Esto es similar al amplificador cascode de la Figura\(\PageIndex{2}\) (a), pero ahora el voltaje en

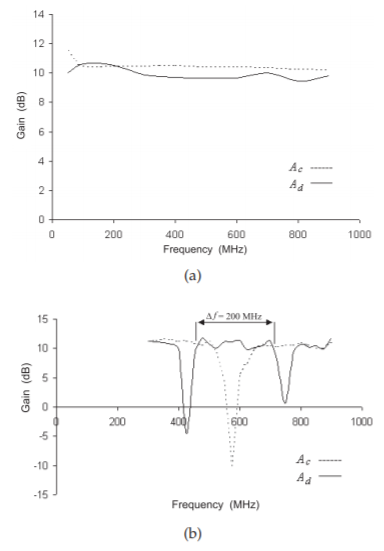

Figura\(\PageIndex{1}\): Ganancia de modo común medida\(A_{c}\), y ganancia de modo diferencial,\(A_{d}\): (a) con circuito de polarización basado en inductores con inductores agrupados de\(0.75\:\mu\text{H}\); y (b) con circuito de polarización tipo balun sin condensadores agrupados.

la puerta del transistor superior,\(V_{G1}\), se selecciona para que se presente una resistencia variable al transistor inferior, así se puede variar la ganancia de voltaje del circuito. Este es un amplificador de ganancia variable.

Los circuitos FET casi siempre están polarizados por corriente, por lo que los circuitos que realizan fuentes de corriente y coincidencia de corriente son particularmente importantes. Se puede usar un solo MOSFET para realizar una fuente de corriente. Si el voltaje puerta a fuente de un MOSFET es fijo, se realiza una fuente de corriente casi constante (vea la ecuación de corriente drenaje-fuente, Ecuación (1.3.17)). En la Figura\(\PageIndex{2}\) (d) se muestra un circuito amplificador diferencial con una fuente de corriente variable. Lo que es particularmente interesante es que el transistor que controla la polarización a la fuente de corriente puede ser parte de un circuito digital, permitiendo el control digital de la polarización del circuito analógico. El concepto se puede replicar reemplazando\(M_{1}\) por múltiples transistores en paralelo con cada transistor teniendo una señal binaria en la puerta. Este es un componente fundamental en el control digital de circuitos analógicos, incluidos los RFIC. Por ejemplo, los RFIC modernos incorporan un recorte controlado digitalmente de los RFIC para lograr, por ejemplo, un mejor\(IQ\) equilibrio de moduladores en cuadratura.

Otro circuito que controla la corriente en un RFIC es el espejo de corriente mostrado en la Figura\(\PageIndex{2}\) (c). En este circuito,\(I_{1} = I_{2}\), como los voltajes puerta-fuente de los transistores\(M_{1}\) y\(M_{2}\) son los mismos. La conexión de drenaje-puerta de\(M_{1}\) asegura

Figura\(\PageIndex{2}\): Circuitos analógicos MOS: (a) amplificador cascode; (b) amplificador cascode de ganancia variable; (c) espejo de corriente; (d) par diferencial; (e) implementación de tripletes multi-tanh de un par diferencial que proporciona linealidad mejorada.

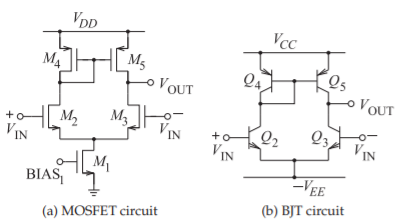

Figura\(\PageIndex{3}\): Circuitos de par diferencial cada uno con un espejo de corriente.

que el voltaje puerta-fuente será lo que sea necesario para soportar la corriente\(I_{1}\) derivada del resto del circuito.

En la Figura\(\PageIndex{3}\) (a) se muestra un amplificador diferencial CMOS con una carga de espejo de corriente. En esta configuración el espejo de corriente presenta una alta impedancia diferencial. Si la impedancia de carga presentada al terminal, etiquetada\(V_{\text{OUT}}\), es menor que esta carga, entonces el amplificador diferencial cargado en espejo actual realiza una salida de un solo extremo al tiempo que tiene la funcionalidad esencial de un circuito diferencial para rechazar señales de modo común. Hay un precio a pagar por esta funcionalidad. El circuito de la Figura\(\PageIndex{3}\) (a) tiene tres caídas de voltaje drenaje-fuente entre los rieles. Esto reduce la disponibilidad

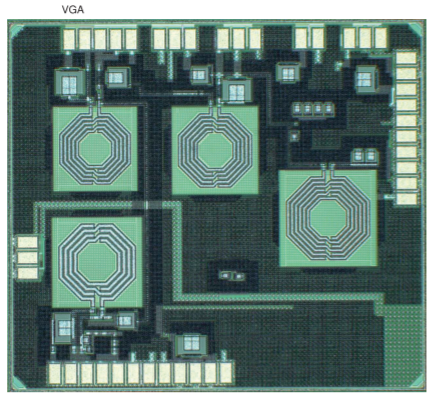

Figura\(\PageIndex{4}\): Fotomicrografía de un transmisor\(90\text{ nm}\) CMOS WCDMA que muestra (MIXER) el mezclador de conversión ascendente y el divisor LO en cuadratura; (VGA) el amplificador de ganancia variable cascode; y el amplificador excitador de dos etapas con potencia de\(9.6\text{ dBm}\) salida. El tamaño de la matriz es\(1.1\text{ mm }\times\: 1.4\text{ mm}\). Después de Yang [21], y Yang y Gard [12]. Copyright K. Gard y X. Yang, utilizados con permiso.

oscilación de voltaje. Este es uno de los principales problemas que se encuentran con los RFIC, ya que la tensión de alimentación viene dictada por las tensiones de suministro relativamente bajas que se pueden soportar en un proceso que está optimizado para circuitos digitales de baja tensión. Un espejo de corriente también se puede realizar usando BJT con el par diferencial cargado por espejo de corriente basado en BJT que se muestra en la Figura\(\PageIndex{3}\) (b) como ejemplo.

Matemáticamente, la característica de entrada/salida simplificada de un MOSFET es esencialmente cuadrática (ver Ecuación (1.3.17)). Es un reto tomar modelos algebraicos tan fundamentales y derivar las ecuaciones que describen el funcionamiento de un circuito completo; un reto que debe abordarse en la síntesis de un circuito con distorsión y rendimiento de ruido especificados. Se puede demostrar que la relación entre la corriente de drenaje y la tensión drenaje-fuente tiene la forma de una función tanh [10]. En cuanto a la transconductancia,\(g_{m}\), aparece como una función cuadrática con un valor pico a una tensión de drenaje que es controlada por la\(W/L\) relación. Al poner varios pares diferenciales en paralelo, teniendo cada par\(W/L\) relaciones escalonadas, se puede realizar un amplificador diferencial compuesto con linealidad mejorada [11, 12]. Este circuito es conocido como un par diferencial multi-tanh. En la Figura\(\PageIndex{2}\) (e) se muestra un par diferencial multitanh triplete. El diseño detallado de RFIC implica la derivación algebraica de las condiciones requeridas. Esta síntesis de redes aplicada a los RFIC se explora en numerosas referencias [13, 14, 15, 16, 17, 18, 19, 20] así como un gran número de trabajos sobre el diseño de RFIC. La síntesis para controlar la distorsión y el ruido está en el corazón del diseño de RFIC. La recopilación de nuevas topologías de circuitos y las técnicas para sintetizarlas (por ejemplo, a partir de conferencias y revistas y patentes), es una parte esencial del diseño de RFIC; que no es tan diferente del proceso para todas las demás formas de diseño de circuitos.

La figura\(\PageIndex{4}\) es una fotomicrografía de un transmisor\(90\text{ nm}\) WCDMA. El diseño consta de tres bloques: un mezclador de conversión ascendente (MIXER), un amplificador cascode de ganancia variable (VGA) y un amplificador de controlador de dos etapas. El

Figura\(\PageIndex{5}\): Amplificador de tres etapas del receptor WCDMA mostrado en la Figura\(\PageIndex{4}\): (a) un amplificador cascode de ganancia variable; y (b) el amplificador excitador de dos etapas. Después de Yang [21], y Yang y Gard [12]. Copyright K. Gard y X. Yang, utilizados con permiso.

esquema de las etapas del amplificador de salida se muestra en la Figura\(\PageIndex{5}\). El amplificador de ganancia variable, el bloque VGA, es un amplificador cascode con polarización variable del FET superior en el cascode para realizar una ganancia variable. Cada uno de los amplificadores en el amplificador excitador de dos etapas tiene un diferente\(V_{DD}\) para que las no linealidades de las dos etapas se puedan diseñar para cancelar, y así se linealiza el rendimiento general del amplificador excitador [12, 21].