2.12: Técnicas de fabricación de semiconductores

- Page ID

- 153717

\( \newcommand{\vecs}[1]{\overset { \scriptstyle \rightharpoonup} {\mathbf{#1}} } \)

\( \newcommand{\vecd}[1]{\overset{-\!-\!\rightharpoonup}{\vphantom{a}\smash {#1}}} \)

\( \newcommand{\id}{\mathrm{id}}\) \( \newcommand{\Span}{\mathrm{span}}\)

( \newcommand{\kernel}{\mathrm{null}\,}\) \( \newcommand{\range}{\mathrm{range}\,}\)

\( \newcommand{\RealPart}{\mathrm{Re}}\) \( \newcommand{\ImaginaryPart}{\mathrm{Im}}\)

\( \newcommand{\Argument}{\mathrm{Arg}}\) \( \newcommand{\norm}[1]{\| #1 \|}\)

\( \newcommand{\inner}[2]{\langle #1, #2 \rangle}\)

\( \newcommand{\Span}{\mathrm{span}}\)

\( \newcommand{\id}{\mathrm{id}}\)

\( \newcommand{\Span}{\mathrm{span}}\)

\( \newcommand{\kernel}{\mathrm{null}\,}\)

\( \newcommand{\range}{\mathrm{range}\,}\)

\( \newcommand{\RealPart}{\mathrm{Re}}\)

\( \newcommand{\ImaginaryPart}{\mathrm{Im}}\)

\( \newcommand{\Argument}{\mathrm{Arg}}\)

\( \newcommand{\norm}[1]{\| #1 \|}\)

\( \newcommand{\inner}[2]{\langle #1, #2 \rangle}\)

\( \newcommand{\Span}{\mathrm{span}}\) \( \newcommand{\AA}{\unicode[.8,0]{x212B}}\)

\( \newcommand{\vectorA}[1]{\vec{#1}} % arrow\)

\( \newcommand{\vectorAt}[1]{\vec{\text{#1}}} % arrow\)

\( \newcommand{\vectorB}[1]{\overset { \scriptstyle \rightharpoonup} {\mathbf{#1}} } \)

\( \newcommand{\vectorC}[1]{\textbf{#1}} \)

\( \newcommand{\vectorD}[1]{\overrightarrow{#1}} \)

\( \newcommand{\vectorDt}[1]{\overrightarrow{\text{#1}}} \)

\( \newcommand{\vectE}[1]{\overset{-\!-\!\rightharpoonup}{\vphantom{a}\smash{\mathbf {#1}}}} \)

\( \newcommand{\vecs}[1]{\overset { \scriptstyle \rightharpoonup} {\mathbf{#1}} } \)

\( \newcommand{\vecd}[1]{\overset{-\!-\!\rightharpoonup}{\vphantom{a}\smash {#1}}} \)

\(\newcommand{\avec}{\mathbf a}\) \(\newcommand{\bvec}{\mathbf b}\) \(\newcommand{\cvec}{\mathbf c}\) \(\newcommand{\dvec}{\mathbf d}\) \(\newcommand{\dtil}{\widetilde{\mathbf d}}\) \(\newcommand{\evec}{\mathbf e}\) \(\newcommand{\fvec}{\mathbf f}\) \(\newcommand{\nvec}{\mathbf n}\) \(\newcommand{\pvec}{\mathbf p}\) \(\newcommand{\qvec}{\mathbf q}\) \(\newcommand{\svec}{\mathbf s}\) \(\newcommand{\tvec}{\mathbf t}\) \(\newcommand{\uvec}{\mathbf u}\) \(\newcommand{\vvec}{\mathbf v}\) \(\newcommand{\wvec}{\mathbf w}\) \(\newcommand{\xvec}{\mathbf x}\) \(\newcommand{\yvec}{\mathbf y}\) \(\newcommand{\zvec}{\mathbf z}\) \(\newcommand{\rvec}{\mathbf r}\) \(\newcommand{\mvec}{\mathbf m}\) \(\newcommand{\zerovec}{\mathbf 0}\) \(\newcommand{\onevec}{\mathbf 1}\) \(\newcommand{\real}{\mathbb R}\) \(\newcommand{\twovec}[2]{\left[\begin{array}{r}#1 \\ #2 \end{array}\right]}\) \(\newcommand{\ctwovec}[2]{\left[\begin{array}{c}#1 \\ #2 \end{array}\right]}\) \(\newcommand{\threevec}[3]{\left[\begin{array}{r}#1 \\ #2 \\ #3 \end{array}\right]}\) \(\newcommand{\cthreevec}[3]{\left[\begin{array}{c}#1 \\ #2 \\ #3 \end{array}\right]}\) \(\newcommand{\fourvec}[4]{\left[\begin{array}{r}#1 \\ #2 \\ #3 \\ #4 \end{array}\right]}\) \(\newcommand{\cfourvec}[4]{\left[\begin{array}{c}#1 \\ #2 \\ #3 \\ #4 \end{array}\right]}\) \(\newcommand{\fivevec}[5]{\left[\begin{array}{r}#1 \\ #2 \\ #3 \\ #4 \\ #5 \\ \end{array}\right]}\) \(\newcommand{\cfivevec}[5]{\left[\begin{array}{c}#1 \\ #2 \\ #3 \\ #4 \\ #5 \\ \end{array}\right]}\) \(\newcommand{\mattwo}[4]{\left[\begin{array}{rr}#1 \amp #2 \\ #3 \amp #4 \\ \end{array}\right]}\) \(\newcommand{\laspan}[1]{\text{Span}\{#1\}}\) \(\newcommand{\bcal}{\cal B}\) \(\newcommand{\ccal}{\cal C}\) \(\newcommand{\scal}{\cal S}\) \(\newcommand{\wcal}{\cal W}\) \(\newcommand{\ecal}{\cal E}\) \(\newcommand{\coords}[2]{\left\{#1\right\}_{#2}}\) \(\newcommand{\gray}[1]{\color{gray}{#1}}\) \(\newcommand{\lgray}[1]{\color{lightgray}{#1}}\) \(\newcommand{\rank}{\operatorname{rank}}\) \(\newcommand{\row}{\text{Row}}\) \(\newcommand{\col}{\text{Col}}\) \(\renewcommand{\row}{\text{Row}}\) \(\newcommand{\nul}{\text{Nul}}\) \(\newcommand{\var}{\text{Var}}\) \(\newcommand{\corr}{\text{corr}}\) \(\newcommand{\len}[1]{\left|#1\right|}\) \(\newcommand{\bbar}{\overline{\bvec}}\) \(\newcommand{\bhat}{\widehat{\bvec}}\) \(\newcommand{\bperp}{\bvec^\perp}\) \(\newcommand{\xhat}{\widehat{\xvec}}\) \(\newcommand{\vhat}{\widehat{\vvec}}\) \(\newcommand{\uhat}{\widehat{\uvec}}\) \(\newcommand{\what}{\widehat{\wvec}}\) \(\newcommand{\Sighat}{\widehat{\Sigma}}\) \(\newcommand{\lt}{<}\) \(\newcommand{\gt}{>}\) \(\newcommand{\amp}{&}\) \(\definecolor{fillinmathshade}{gray}{0.9}\)El silicio es el segundo elemento más común en la corteza terrestre en forma de dióxido de silicio\(\ce{SiO2}\), también conocido como arena de sílice. El silicio se libera del dióxido de silicio por reducción con carbono en un horno de arco eléctrico.

\[\ce{SIO2 + C -> CO2 + Si}\]

Dicho silicio de grado metalúrgico es adecuado para su uso en laminaciones de transformadores de acero al silicio, pero no lo suficientemente puro para aplicaciones de semiconductores. La conversión al cloruro\(\ce{SiCl4}\) (o\(\ce{SiHCl3}\)) permite la purificación por destilación fraccionada. La reducción por zinc ultrapuro o magnesio produce silicio esponjoso, requiriendo purificación adicional. O bien, la descomposición térmica en un calentador de varilla de silicio policristalino caliente por hidrógeno produce silicio ultra puro.

\[\ce{Si + 3HCl -> SiHCl3 + H2}\]

\[\ce{SiHCl3 + H2 -> Si + 3HCl2}\]

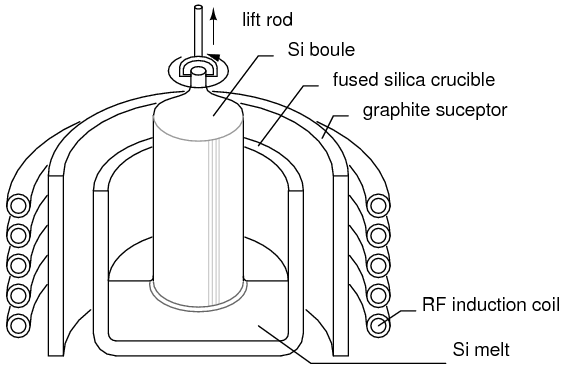

El silicio policristalino se funde en un crisol de sílice fundida calentado por un susceptor de grafito calentado por inducción. El calentador de grafito puede alternativamente ser accionado directamente por un bajo voltaje a alta corriente. En el proceso de Czochralski, la masa fundida de silicio se solidifica en una varilla de silicio monocristalino del tamaño de un lápiz con la orientación deseada de la red cristalina. (Figura abajo) La varilla se gira y se tira hacia arriba a una velocidad para fomentar que el diámetro se expanda a varias pulgadas. Una vez que se alcanza este diámetro, la bola se tira automáticamente a una velocidad para mantener un diámetro constante a una longitud de unos pocos pies. Se pueden añadir dopantes a la masa fundida del crisol para crear, por ejemplo, un semiconductor de tipo P. El aparato de cultivo está encerrado dentro de una atmósfera inerte.

Crecimiento de silicio monocristalino Czochralski.

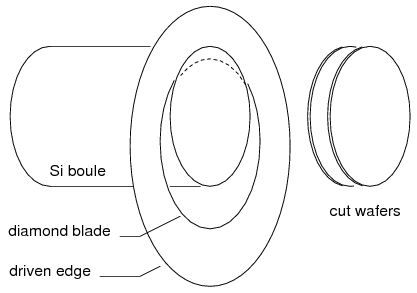

El boule terminado se muele a un diámetro final preciso y los extremos se recortan. El boule es cortado en obleas por una sierra diamantada de diámetro interior. Las obleas se muelen planas y pulidas. Las obleas podrían tener una capa epitaxial tipo N cultivada encima de la oblea por deposición térmica para mayor calidad. Las obleas en esta etapa de fabricación son entregadas por el fabricante de obleas de silicio al fabricante de semiconductores.

El boule de silicio es diamante aserrado en obleas.

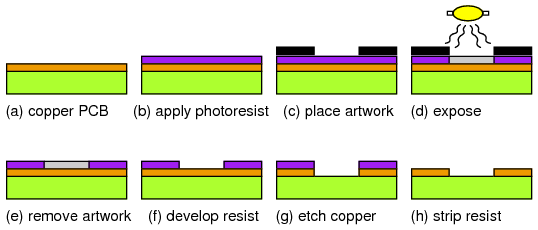

El procesamiento de semiconductores implica fotolitografía, un proceso para la fabricación de planchas de impresión litográfica metálica mediante grabado ácido. La versión basada en electrónica de esto es el procesamiento de placas de circuito impreso de cobre. Esto se revisa en la Figura siguiente como una introducción fácil a la fotolitografía involucrada en el procesamiento de semiconductores.

El procesamiento de placas de circuito impreso de cobre es similar a las etapas fotolitográficas del procesamiento de semiconductores.

Comenzamos con una lámina de cobre laminada a una placa de fibra de vidrio epoxi en la Figura anterior (a). También necesitamos obras de arte positivas con líneas negras correspondientes a las líneas de cableado de cobre y almohadillas que deben permanecer en la placa terminada. Se requiere una obra de arte positiva porque se usa una resistencia de acción positiva. Sin embargo, la resistencia negativa está disponible tanto para placas de circuito como para procesamiento de semiconductores. En (b) la fotoresistencia positiva líquida se aplica a la cara de cobre de la placa de circuito impreso (PCB). Se deja secar y se puede hornear en un horno. La obra de arte puede ser una reproducción positiva de película plástica de la obra de arte original escalada al tamaño requerido. La obra de arte se coloca en contacto con la placa de circuito debajo de una placa de vidrio en (c). El tablero se expone a la luz ultravioleta (d) para formar una imagen latente de fotoresistencia ablandada. La obra de arte se retira (e) y la resistencia ablandada se lava con una solución alcalina (f). La placa de circuito enjuagada y seca (horneada) tiene una imagen de resistencia endurecida encima de las líneas de cobre y las almohadillas que deben permanecer después del grabado. El tablero se sumerge en el grabante (g) para eliminar el cobre no protegido por resistencia endurecida. La placa grabada se enjuaga y la capa protectora se elimina con un disolvente.

La principal diferencia en el patrón de los semiconductores es que una capa de dióxido de silicio encima de la oblea toma el lugar de la resistencia durante las etapas de procesamiento a alta temperatura. Sin embargo, la resistencia es necesaria en el procesamiento húmedo a baja temperatura para modelar el dióxido de silicio.

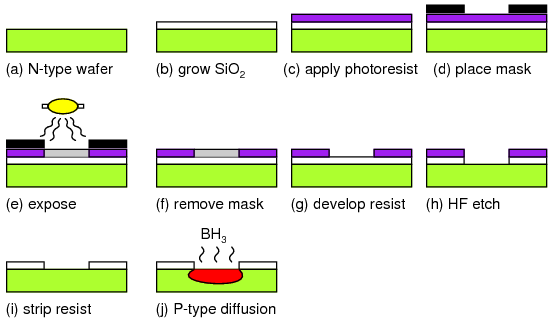

Una oblea de silicio dopado tipo N en la Figura siguiente (a) es el material de partida en la fabricación de uniones semiconductoras. Una capa de dióxido de silicio (b) se cultiva encima de la oblea en presencia de oxígeno o vapor de agua a alta temperatura (más de 1000 o C en un horno de difusión. Se aplica un charco de resistencia al centro de la oblea enfriada, luego se hace girar en un mandril de vacío para distribuir uniformemente la capa resistente. El protector horneado (c) tiene una máscara de cromo sobre vidrio aplicada a la oblea en (d). Esta máscara contiene un patrón de ventanas que se expone a la luz ultravioleta (e).

Fabricación de una unión de diodo de silicio.

Después de retirar la máscara en la Figura anterior (f), la resistencia positiva se puede desarrollar (g) en una solución alcalina, abriendo ventanas en la capa resistente ablandada UV. El propósito de la resistencia es proteger el dióxido de silicio del grabado de ácido fluorhídrico (h), dejando solo ventanas abiertas correspondientes a las aberturas de la máscara. El material resistente restante (i) se desprende de la oblea antes de regresar al horno de difusión. La oblea se expone a un dopante gaseoso tipo P a alta temperatura en un horno de difusión (j). El dopante solo se difunde en el silicio a través de las aberturas en la capa de dióxido de silicio. Cada difusión P a través de una abertura produce una unión PN. Si los diodos fueran el producto deseado, la oblea se trazaría con diamante y se rompería en chips de diodo individuales. Sin embargo, toda la oblea puede procesarse adicionalmente en transistores de unión bipolar.

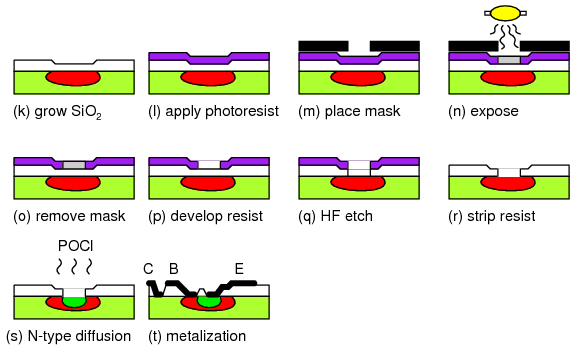

Para convertir los diodos en transistores, se requiere una pequeña difusión tipo N en el medio de la región P existente. Repetir los pasos anteriores con una máscara que tiene aberturas más pequeñas logra esto. Aunque no se muestra en la Figura anterior (j), probablemente se formó una capa de óxido en esa etapa durante la difusión P. La capa de óxido sobre la difusión P se muestra en la Figura siguiente (k). Se aplica fotoresistencia positiva y se seca (l). Se aplica la máscara de emisor de cromo sobre vidrio (m), y se expone a UV (n). Se quita la máscara (o). La resistencia ablandada UV en la abertura del emisor se elimina con una solución alcalina (p). El dióxido de silicio expuesto es grabado con ácido fluorhídrico (HF) en (q)

Fabricación de un transistor de unión bipolar, continuación de Fabricación de una unión de diodo de silicio.

Después de que la capa resistente no expuesta es despojada de la oblea (r), se coloca en un horno de difusión (Figura anterior (s) para procesamiento a alta temperatura. Un dopante gaseoso tipo N, como el oxicloruro de fósforo (POCl), se difunde a través de la pequeña ventana del emisor en el (los) óxido (s). Esto crea capas NPN correspondientes al emisor, base y colector de un BJT. Es importante que el emisor tipo N no sea conducido todo el camino a través de la base tipo P, cortocircuitando el emisor y el colector. La región base entre el emisor y el colector también necesita ser delgada para que el transistor tenga un β útil. De lo contrario, una región base gruesa podría formar un par de diodos en lugar de un transistor. En (t) se muestra metalización haciendo contacto con las regiones del transistor. Esto requiere una repetición de los pasos anteriores (no mostrados aquí) con una máscara para aberturas de contacto a través del óxido. Otra repetición con otra máscara define el patrón de metalización encima del óxido y en contacto con las regiones del transistor a través de las aberturas.

La metalización podría conectar numerosos transistores y otros componentes en un circuito integrado. Sin embargo, solo se muestra un transistor. La oblea terminada está rayada con diamante y rota en troqueles individuales para su empaque. El alambre de aluminio de calibre fino une los contactos metalizados en la matriz a un marco de plomo, lo que saca los contactos del paquete final.

Revisar

- La mayoría de los semiconductores están basados en silicio ultra puro porque forma un óxido de vidrio encima de la oblea. Este óxido se puede modelar con fotolitografía, haciendo posibles circuitos integrados complejos.

- Cristales individuales de silicio en forma de salchicha se cultivan por el proceso Czochralski, Estos son aserrados de diamante en obleas.

- El patrón de obleas de silicio por fotolitografía es similar al patrón de placas de circuito impreso de cobre. La fotorresistencia se aplica a la oblea, que se expone a la luz UV a través de una máscara. Se desarrolla la capa protectora, luego se graba la oblea.

- ácido fluorhídrico grabado abre ventanas en el dióxido de silicio protector encima de la oblea.

- La exposición a dopantes gaseosos a alta temperatura produce uniones semiconductoras definidas por las aberturas en la capa de dióxido de silicio.

- La fotolitografía se repite para más difusiones, contactos y metalización.

- La metalización puede interconectar múltiples componentes en un circuito integrado.