5.4: La CPU

- Page ID

- 80648

La CPU reúne todos los componentes en un solo paquete para ejecutar programas. La CPU en este texto consta de dos subsecciones, y fue diseñada a propósito para ser lo suficientemente simple como para que los cables de control (distintos del reloj) para cada subsección de la CPU estén completamente separados de la otra.

La primera subsección hace toda la aritmética y administra la entrada/salida a/desde la memoria de datos. Esta subsección utiliza los cables de control Clock, memWr (write memory), clRac (borre $ac configurándolo en 0), writeAC (escriba un valor a $ac), AluSrc (elija una fuente para el segundo operando ALU, ya sea una memoria o un valor inmediato) y AluOpt (un valor de 4 bits para especificar qué operación ejecutar sobre la ALU).

WriteAC (escriba un valor en $ac), AluSrc (elija una fuente para el segundo operando ALU, ya sea una memoria o un valor inmediato) y AluOpt (un valor de 4 bits para especificar qué operación ejecutar en la ALU).

Estas dos subsecciones se verán por separado.

Antes de comenzar, un 0 en un cable de control implica no hacer nada, de ahí que una instrucción noop sea un 0x0000 de 2 bytes. Si no se está utilizando un cable, por defecto configúrelo en 0.

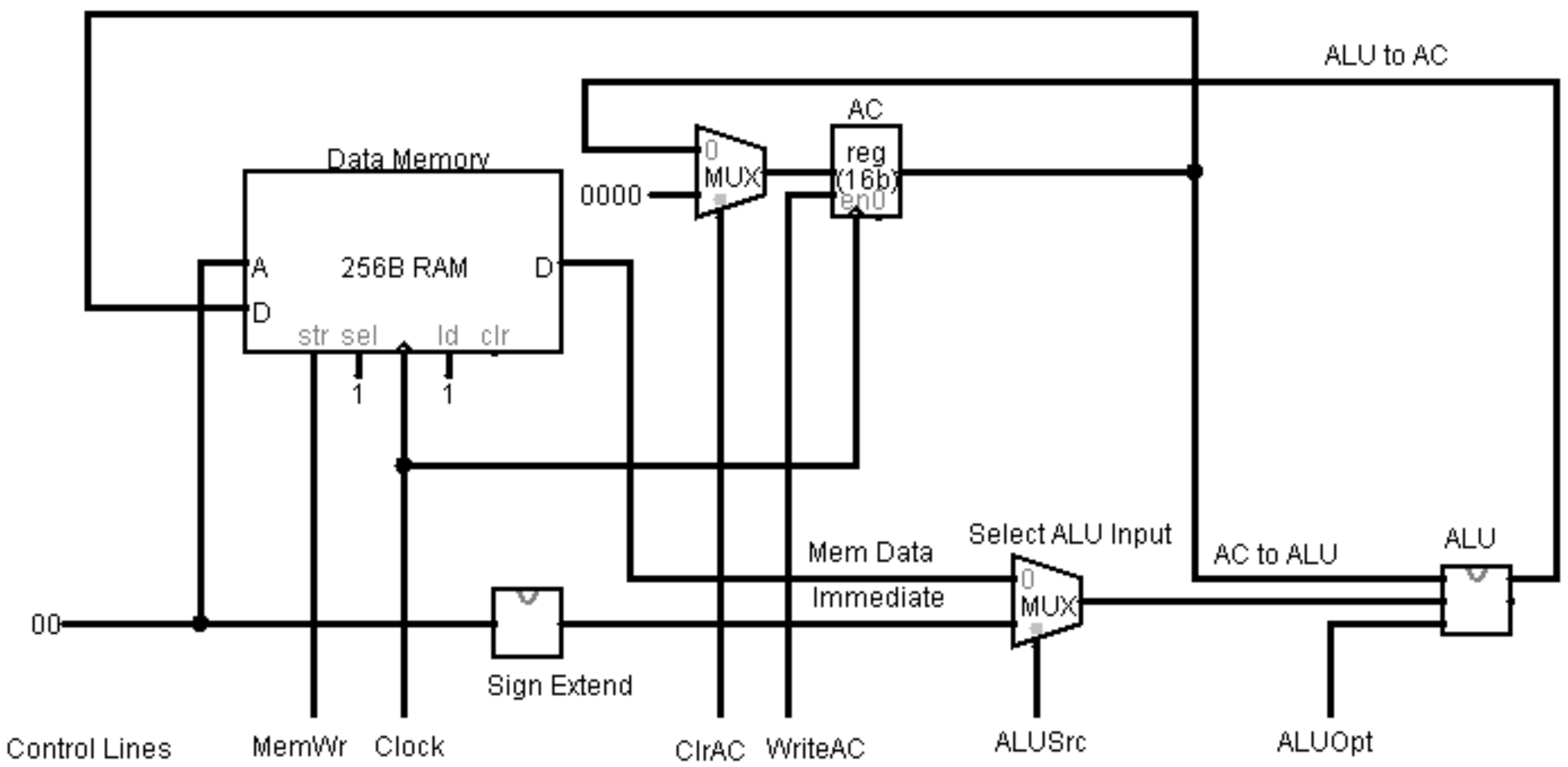

5.4.1 La CPU — Subsección Aritmética

La subsección aritmética de la CPU cubre el registro $ac, la ALU y la memoria de datos. Esto cubrirá las operaciones de Ensamblaje clac, add, addi, sub, subi, y stor. La subsección aritmética se muestra en el siguiente diagrama.

La operación clac selecciona la entrada constante 0x0000 usando el mux frente al $ac para establecer el valor del $ac. Para ello, la línea CLRac al mux es 1 (seleccionando 0x0000) y la línea WriteAC es 1. Todas las demás líneas de control son 0.

Para las operaciones add y sub, la entrada a la ALU son datos de memoria, por lo que la línea AluSrc se establece en 0 para seleccionar los Datos Mem. El resultado se vuelve a almacenar en el $ac, por lo que la línea CLRac debe establecerse en 0 para seleccionar la salida de la ALU, y la línea WriteAC se establece en 1 para escribir el resultado de ALU en el AC. El AluOpt se establece en 0000 para sumar y 0001 para restar. Todas las demás líneas de control se establecen en 0.

Para las operaciones addi y subi, la entrada a la ALU es el valor inmediato, fo la línea AluSc se establece en 1 para seleccionar el valor de datos inmediato. Todas las demás líneas se establecen como las operaciones add y sub.

Para la operación stor, el memWR se establece en 1, que escribe el valor en el puerto D en la memoria de datos en la memoria en la dirección especificada en el puerto A (tenga en cuenta que la dirección proviene de la parte inmediata de la instrucción). Todas las demás líneas de control se establecen en 0.

Algunos lectores podrían estar preocupados de que haya valores pasados en la CPU que no se utilicen. Por ejemplo, cuando se está ejecutando la operación stor, todavía se calcula un valor en la ALU, y se envía por cable al $ac. Sin embargo, la línea WriteAC es 0, por lo que el valor ALU no tiene ningún efecto y se ignora. Lo mismo ocurre con el valor de Mem Data para operaciones inmediatas como addi. Se genera el Mem Data, pero se ignora ya que el AluSc elige el valor inmediato. Muchas líneas se establecen en cada instrucción, y la mayoría de ellas son ignoradas, razón por la cual usar configurando todos los cables de control en 0 una instrucción NOOP no hace nada.

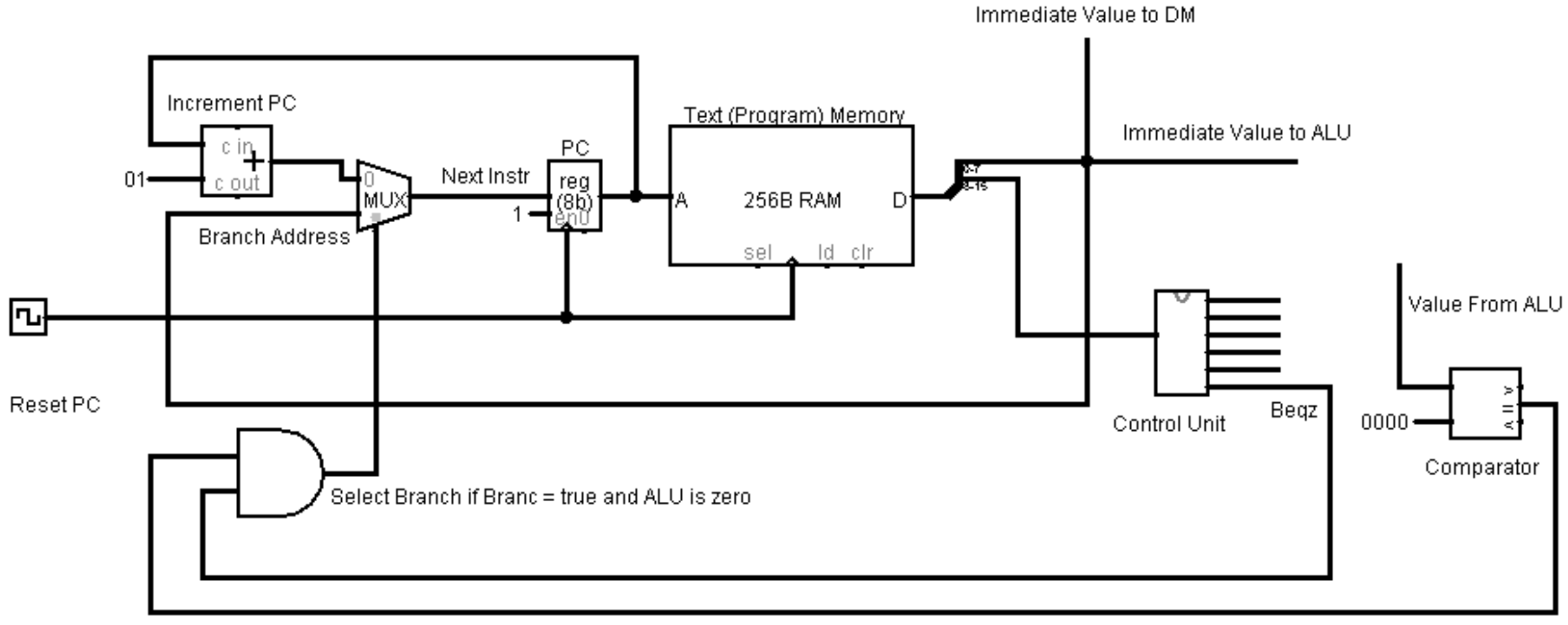

5.4.2 La CPU — Subsección de Ruta de Ejecución

La segunda subsección de la CPU es la ruta de ejecución, que se muestra en la siguiente figura.

Como muestra esta figura, el valor del registro $pc se utiliza para establecer la dirección de lectura para la instrucción. Esta instrucción se divide entonces en la mitad de control (bits 8-15) y el valor inmediato (bits 0-7). Los bits de control se envían a la CU para establecer los cables de control, y el valor inmediato se envía a la memoria de datos o a la ALU para su uso en la subsección aritmética de la CPU.

Cada vez que se ejecuta una instrucción, el registro $pc se cambia para apuntar a la siguiente instrucción a ejecutar. Cuando el programa se ejecuta secuencialmente, se selecciona la siguiente instrucción en la memoria agregando 1 al $pc en el nombre del sumador Increment PC, y el multiplexor se establece en 0 para seleccionar esta instrucción.

La única vez que no se selecciona la siguiente instrucción es si el cable Beqz es alto (es decir, esta es una instrucción beqz), Y los resultados del compactador son 1 (la ALU tiene un valor de 0). Cuando esto sucede, el mux selecciona la Dirección de Sucursal, que es el valor inmediato de la instrucción, y el programa continúa ejecutándose en la instrucción en la nueva dirección.