12.5: Conversión de analógico a digital

- Page ID

- 87822

Ahora que conoce los conceptos básicos detrás de la conversión digital a analógica, podemos examinar el sistema inverso, la conversión de analógico a digital. El proceso de conversión analógico a digital a veces se denomina cuantificación, lo que implica los pasos discretos individuales que asume la salida. Existen varias técnicas para producir la conversión. Algunas técnicas están optimizadas para la velocidad de conversión más rápida posible y otras para la mayor precisión. Investigaremos los tipos más populares.

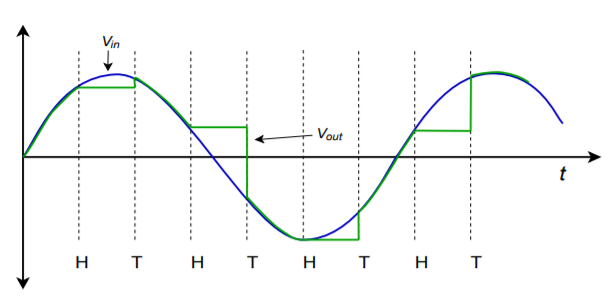

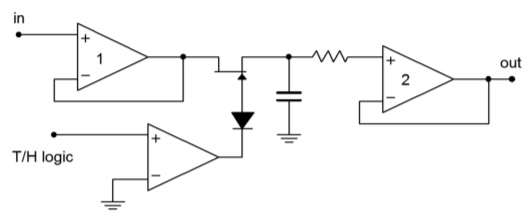

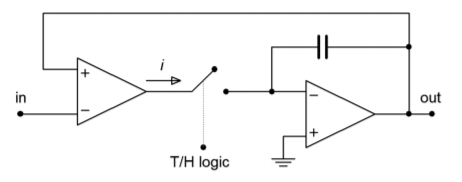

El concepto de conversión AD es bastante simple: desea medir el voltaje de la forma de onda entrante en instancias específicas en el tiempo. Esta medición se traducirá en una palabra digital. Una limitación práctica es el hecho de que la circuitería de conversión puede requerir una pequeña cantidad de tiempo de cálculo o traducción. Para obtener la máxima precisión, entonces, es importante que la forma de onda medida no cambie durante el intervalo de conversión. Para ello, se utilizan subcircuitos especializados llamados amplificadores de seguimiento y retención (o de muestreo y retención). Por lo general, se abrevian como T/H o S/H. Su trabajo es capturar un potencial de entrada y producir una salida constante para alimentar al convertidor AD. El símbolo esquemático T/H se muestra en la Figura\(\PageIndex{1}\). Cuando la lógica T/H está en modo pista, el circuito actúa como un búfer simple, por lo que su voltaje de salida es igual a su entrada. Cuando la lógica pasa al estado de espera, el voltaje de salida se bloquea en su potencial actual y permanece allí hasta que el circuito vuelve a conmutar al modo de seguimiento. Una representación de esta operación se muestra en la Figura\(\PageIndex{2}\).

Figura\(\PageIndex{1}\): Símbolo para el amplificador de seguimiento y retención.

Figura\(\PageIndex{2}\): Operación de seguimiento y retención.

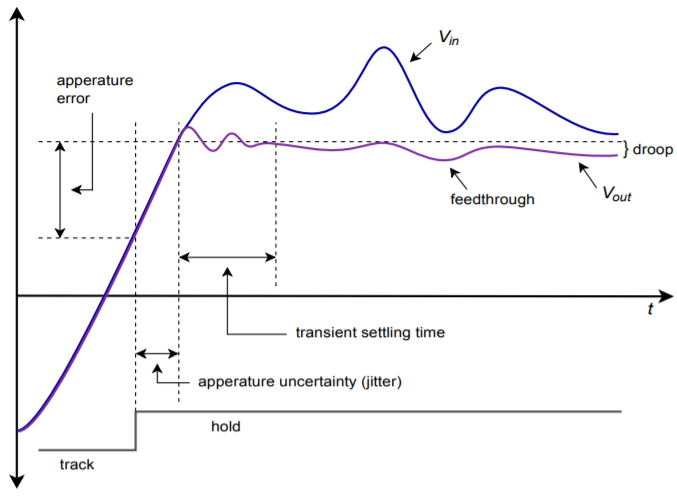

En realidad, el proceso de seguimiento y retención no es perfecto y pueden surgir errores. Estos errores se muestran ampliados en la Figura\(\PageIndex{3}\). En primer lugar, hay un pequeño retraso entre el momento en que cambia la señal lógica y el T/H comienza a reaccionar. La cantidad exacta de tiempo es variable y es responsable del error de apertura. Esto es igual a la diferencia de voltaje entre las señales en los tiempos deseados y reales. Además, debido a la naturaleza dinámica del proceso de conmutación de pista a retención, puede ocurrir algún timbre inicial en la forma de onda de retención.

Figura\(\PageIndex{3}\): Errores de seguimiento y retención.

Se puede ver que a medida que avanza el tiempo, la forma de onda de retención tiende a decairse hacia cero. Esto se debe a que el voltaje retenido generalmente se forma a través de un condensador. Aunque la constante de tiempo de descarga puede ser muy larga, no puede ser infinita y, por lo tanto, la carga finalmente se desangra. Este parámetro se mide por la tasa de caída (unidades fundamentales de voltios por segundo). Por último, existe la posibilidad de error de alimentación. Si se produce un gran cambio en la forma de onda de entrada durante el período de retención, es posible que una parte de la señal pueda “filtrarse” a través de la salida T/H. Estos errores son particularmente problemáticos cuando se trabaja con convertidores de alta resolución. Los sistemas de baja resolución pueden no verse afectados negativamente por estas aberraciones relativamente pequeñas.

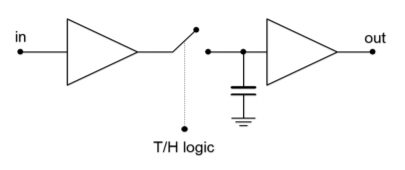

Para crear un T/H, normalmente se utilizan un par de búferes de alta impedancia, junto con alguna forma de elemento de conmutación y un condensador para mantener la carga. Los ejemplos se muestran en la Figura\(\PageIndex{4}\). La figura\(\PageIndex{4a}\) muestra el tipo de voltaje general, T/H de bucle abierto. Los búferes presentan alta impedancia de entrada. Cuando el interruptor está cerrado, el amplificador operacional 1 alimenta directamente el amplificador operacional 2 y, por lo tanto, el voltaje de salida es igual al voltaje de entrada. Normalmente, el condensador de retención es relativamente pequeño y no afecta negativamente a la capacidad de accionamiento del amplificador operacional 1.

Figura\(\PageIndex{4a}\): Circuitos de seguimiento y retención. Modo general de voltaje de bucle abierto de seguimiento y retención.

Una versión más detallada de este circuito se muestra en la Figura\(\PageIndex{4b}\). Cada amplificador operacional es un tipo de entrada FET para un consumo mínimo de corriente de entrada. El interruptor es un JFET simple que es controlado por un comparador.

Figura\(\PageIndex{4b}\): Circuitos de seguimiento y retención. Seguimiento y retención basado en amplificador operacional.

Cuando la lógica T/H es alta, la puerta del JFET es alta, produciendo así una baja onresistance (es decir, un interruptor cerrado). Cuando la salida del comparador va baja, el JFET se apaga creando una alta impedancia (es decir, interruptor abierto). En este estado, el amplificador operacional 2 es alimentado por el condensador de retención y almacena este potencial a su salida. Para una caída mínima, es esencial que el condensador sea un tipo de fuga baja y que el amplificador operacional 2 tenga una corriente de polarización de entrada muy baja (por ejemplo, entrada FET). La resistencia de entrada se usa solo para limitar posibles corrientes de descarga destructivas cuando el circuito está apagado. El diodo situado entre el comparador y el FET se utiliza para evitar que un potencial de salida del comparador positivo excesivamente grande llegue a la puerta del FET y posiblemente lo dañe. (Un comparador alto polarizará inversamente el diodo en serie). La figura\(\PageIndex{4c}\) muestra un circuito alternativo que utiliza un enfoque de circuito cerrado, en modo de corriente. Tenga en cuenta que el condensador de retención ahora forma parte de un integrador. Mientras que la forma de bucle abierto ofrece tiempos de adquisición y asentamiento más rápidos, el sistema de bucle cerrado ofrece un mejor seguimiento de la señal.

Figura\(\PageIndex{4c}\): Circuitos de seguimiento y retención. Modo de corriente de bucle cerrado general de seguimiento y retención.

También es posible un modo de voltaje de bucle cerrado, pero la forma de corriente generalmente ofrece menos problemas con los transitorios de fuga y conmutación. Para trabajos de propósito general, una variedad de amplificadores de seguimiento y retención están disponibles en forma de CI de varios fabricantes.

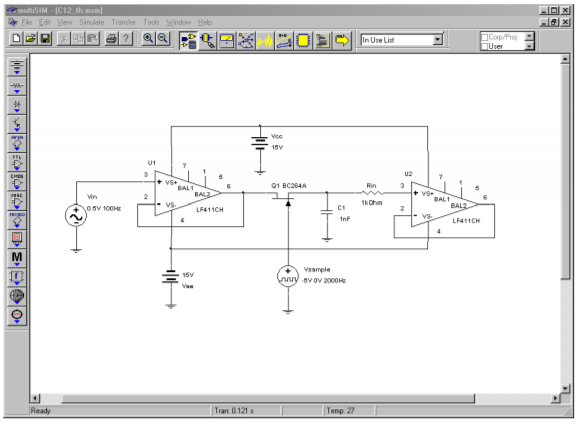

Simulación por Computadora

En la Figura\(\PageIndex{4b}\) se muestra una simulación de un circuito de seguimiento y retención similar al mostrado en la Figura\(\PageIndex{5}\). La señal de entrada de 100 Hz se está muestreando a 2 kHz, o 20 veces por ciclo.

Figura\(\PageIndex{5a}\): Circuito de seguimiento y retención en Multisim.

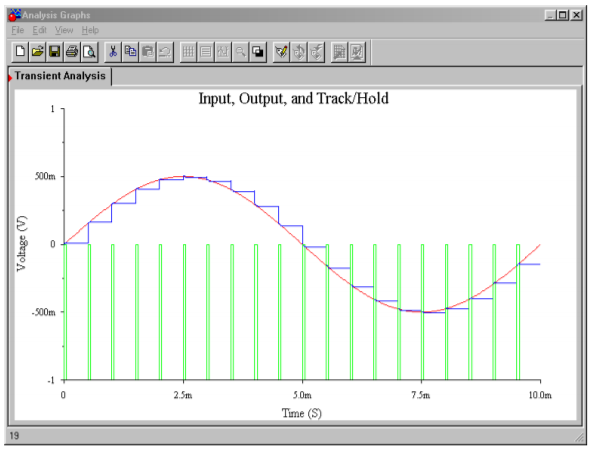

Tres formas de onda de interés se muestran en el gráfico de Análisis Transitorio. La forma de onda de entrada se ve en el centro como la onda sinusoidal que varía suavemente. A lo largo de la parte inferior de la gráfica, se pueden ver picos estrechos. Esta es la señal lógica T/H. La porción alta del pulso (a 0 voltios) es la lógica de la pista, y la señal baja más ancha (cayendo por debajo del límite de -1 voltios del gráfico) representa la lógica de retención. La onda sinusoidal escalonada es el voltaje de salida. Observe cómo el circuito adquiere o rastrea la señal de entrada durante el pulso de pista y luego permanece en ese nivel cuando se aplica la lógica de retención. Es durante estos tiempos de espera que los cálculos serán realizados por el convertidor analógico-digital.

Figura\(\PageIndex{5b}\): Formas de onda Multisim para circuito de seguimiento y retención.

12.5.1: Técnicas de conversión analógico-digital

Varias técnicas diferentes han evolucionado para hacer frente a diferentes requisitos del sistema. Estos incluyen destello, escalera, aproximación sucesiva y formas delta-sigma.

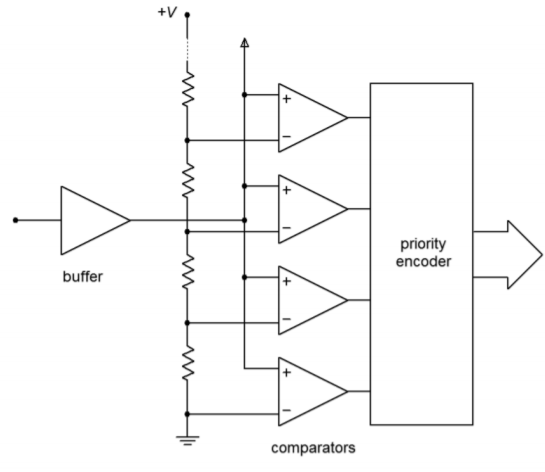

La conversión flash se usa generalmente para trabajos de alta velocidad, como aplicaciones de video. Los circuitos suelen ser de baja resolución. Un convertidor flash se compone de una cadena de comparadores como se muestra en la Figura\(\PageIndex{6}\). La señal de entrada se aplica a todos los comparadores simultáneamente. Cada comparador también está atado en una escalera de referencia. Efectivamente, hay un comparador para cada paso de cuantificación. Cuando se aplica una señal dada, un número de comparadores hacia la parte inferior de la cadena producirán un nivel alto, ya que\(V_{in}\) será mayor que sus referencias. Por el contrario, los comparadores hacia la parte superior indicarán un bajo. El comparador en el que las salidas cambian de alto a bajo indica el valor de paso más cercano a la señal de entrada. El conjunto de salidas del comparador se puede alimentar a un codificador de prioridad que convertirá esta simple secuencia no ponderada en una palabra binaria normal.

Figura\(\PageIndex{6}\): Convertidor flash.

El único retardo de tiempo involucrado en la conversión es el del retardo de propagación lógica. Por lo tanto, esta técnica de conversión es bastante útil para cambiar rápidamente las señales. Su caída radica en el hecho de que se necesita un comparador para cada posible cambio de paso de salida. Un convertidor flash de 8 bits requiere 256 comparadores, mientras que una versión de 16 bits requiere 65,536. Obviamente, esto es bastante excesivo, y las unidades en el rango de 4 a 6 bits son comunes. Aunque la resolución de 6 bits puede parecer al principio demasiado gruesa para cualquier aplicación, en realidad es bastante útil para pantallas de video.

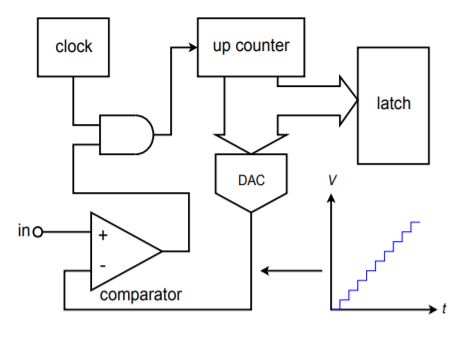

Para trabajos de alta resolución, se debe utilizar alguna otra técnica. Una posibilidad se muestra en la Figura\(\PageIndex{7}\). Esto se llama convertidor de escalera. Su funcionamiento es bastante sencillo. Cuando se inicia una conversión por primera vez, la salida del contador será todo ceros. Esto produce una salida DAC de cero, y por lo tanto, la salida del comparador será alta. El siguiente ciclo de reloj incrementará el contador ascendente, haciendo que la salida DAC aumente en un nivel de paso. Esta señal se compara con la entrada, y si la entrada es mayor, la salida permanecerá alta. El reloj continuará incrementando el contador de esta manera hasta que la salida DAC apenas supere el nivel de entrada. En este punto la salida del comparador cae baja, lo que indica que la conversión está completa. Esta señal se puede usar entonces para bloquear la salida del contador. Este circuito recibe su nombre por el hecho de que la forma de onda producida por el DAC parece una escalera. La técnica de escalera se puede utilizar para la conversión de muy alta resolución, siempre y cuando se utilice un DAC de alta resolución apropiado. El principal problema con esta forma es su muy baja velocidad de conversión, debido a que debe haber tiempo para probar cada combinación de bits posible. En consecuencia, un sistema de 16 bits requiere 65,536 comparaciones. Incluso si se usa un DAC rápido de 1 microsegundo, esto limitaría el intervalo de muestreo a casi 66 milisegundos. Esto se traduce en una frecuencia de entrada máxima antes del aliasing de solo 7 Hz. Al señalar que la frecuencia más baja que la mayoría de los humanos puede escuchar es de unos 20 Hz, esta técnica apenas es adecuada para algo como la grabación de audio digital. De hecho, para trabajos de propósito general, se evita el sistema de escalera en favor de la técnica de aproximación sucesiva.

Figura\(\PageIndex{7}\): Convertidor de escalera.

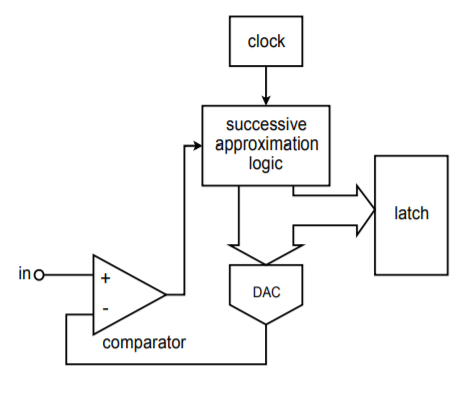

La aproximación sucesiva es una buena solución de propósito general adecuada para sistemas que requieren resoluciones en el área de 16 bits. En lugar de intentar convertir la señal de entrada en un instante como el convertidor flash, esta técnica crea la salida bit a bit. A diferencia del convertidor de escalera, cada nivel individual no necesita ser probado. En su lugar, se utiliza un algoritmo de búsqueda binaria. Podrías pensar en ello como hacer una serie de conjeturas, cada vez acercándose un poco más al resultado. Cada suposición da como resultado una comparación simple. Para una salida de\(n\) -bit, es necesario hacer\(n\) comparaciones.

Figura\(\PageIndex{8}\): Convertidor sucesivo-aproximación.

Un diagrama de bloques de un convertidor de aproximación sucesiva se muestra en la Figura\(\PageIndex{8}\). En lugar de un simple contador ascendente, se utiliza un circuito para implementar el algoritmo de aproximación sucesiva. Así es como funciona el circuito. El primer bit a probar es el bit más significativo. El DAC se alimenta con un 1 con todos los bits restantes establecidos en 0 (es decir,\(100000 \dots )\). Esta palabra representa la mitad del valor máximo capaz por el sistema. La salida del comparador indica si\(V_{in}\) es mayor o menor que la salida DAC resultante. Si la salida del comparador es alta, significa que la salida digital requerida debe ser mayor que la palabra actual. Si la salida del comparador es baja, entonces la palabra digital actual es demasiado grande, por lo que el MSB se establece en 0. En este punto, el siguiente bit más significativo se prueba configurándolo en 1. La nueva palabra se alimenta al DAC, y nuevamente, se usa el comparador para determinar si el bit bajo prueba debe permanecer o no en 1 o ser reajustado. En este punto se han determinado los dos bits más significativos. Los bits restantes se establecen individualmente en 1 y se prueban de manera similar hasta que se determina el bit menos significativo. De esta manera, un sistema de 16 bits sólo requiere 16 comparaciones. Con un DAC de 1 microsegundo, la conversión toma solo 16 microsegundos. Esto se traduce en una frecuencia de muestreo de 62.5 kHz; así se permite una frecuencia máxima de entrada de 31.25 kHz. Como puede ver, esto es mucho más eficiente que la técnica de escalera.

Para las resoluciones más altas combinadas con altas tasas de muestreo, las técnicas de conversión delta-sigma son populares. Básicamente, un convertidor de baja resolución se ejecuta a una velocidad muchas veces mayor que la frecuencia Nyquist (quizás 256 veces mayor). Un filtro digital especial llamado decimador convierte el flujo de datos de alta velocidad de muestreo de baja resolución en una velocidad más baja con mayor resolución. Esta técnica puede lograr conversiones en el rango de 50 kHz con resolución de 20 bits. El diseño y análisis de moduladores delta-sigma y filtros digitales es un tema avanzado más allá del alcance de este texto. Sin embargo, veremos un CI representativo en la siguiente sección.

12.5.2: Circuitos Integrados Convertidores Analógico-Digital

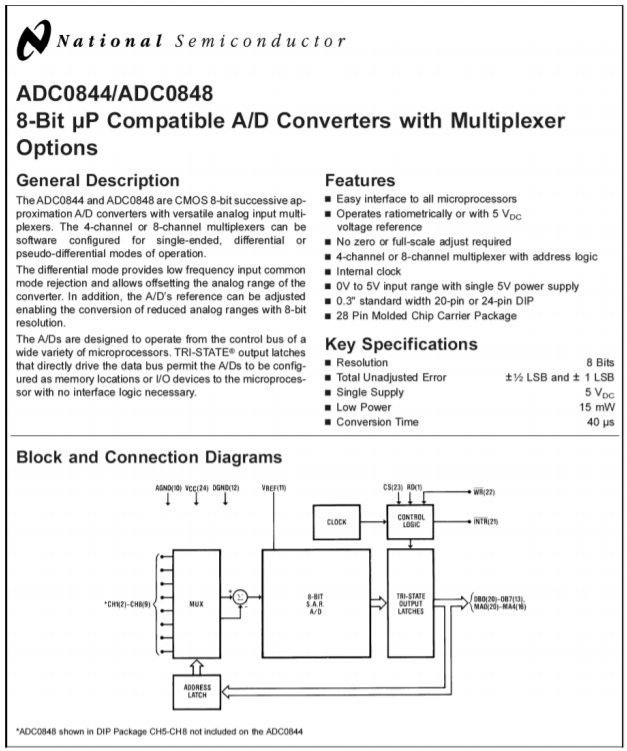

En esta sección examinaremos algunos CI específicos de ADC, junto con aplicaciones seleccionadas. Los CI incluyen el ADC0844, una unidad compatible con microprocesador de 8 bits; el ADC12181, un convertidor muy rápido de 12 bits que utiliza técnicas de canalización; y el CS5396, un convertidor de 24 bits diseñado principalmente para aplicaciones de audio.

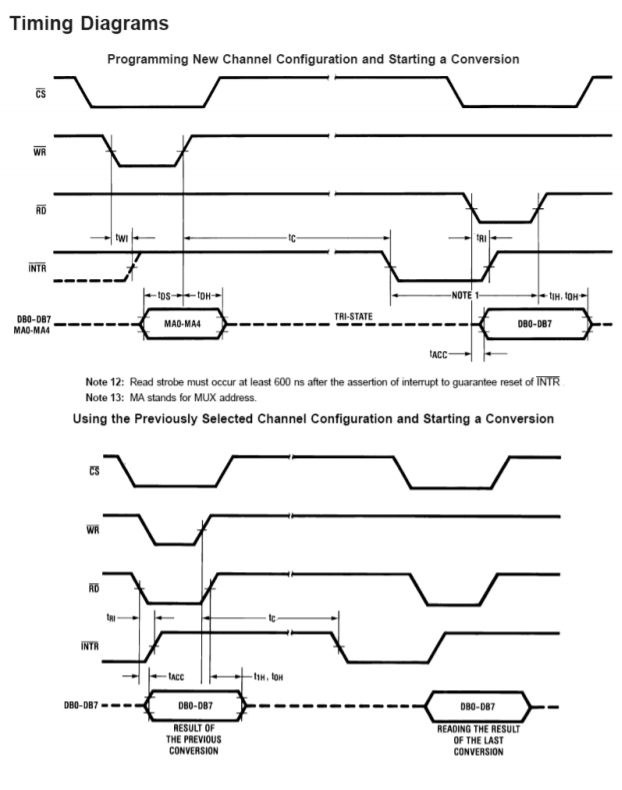

ADC0844

En la Figura se muestra un diagrama de bloques del ADC0844\(\PageIndex{9}\). Junto con el reloj incorporado y el registro de aproximación sucesiva (SAR) de 8 bits, el IC también incluye un multiplexor de entrada, pestillos de tres estados y pines lógicos de lectura, escritura y selección de chip. Esto significa que el ADC0844 se interconecta fácilmente con un bus de datos de microprocesador y puede usarse como un dispositivo de E/S mapeado en memoria. Este IC es un dispositivo de velocidad moderada, mostrando una velocidad de conversión típica de 40 microsegundos. El diagrama de tiempos para el ADC0844 se muestra en la Figura\(\PageIndex{10}\). Se inicia una conversión poniendo bajas las líneas chip-select y write-logic. El borde descendente de escritura restablece el convertidor y su borde ascendente inicia la conversión real. Después del periodo de conversión, que se establece internamente, los datos digitales pueden ser transferidos a los pestillos de salida con la línea readlogic. Tenga en cuenta que la frecuencia de repetición de pulso de la línea lógica de escritura establece la frecuencia de muestreo. Por lo tanto, un pequeño programa que se ejecuta en el microprocesador anfitrión que lee y escribe en el ADC puede usarse para controlar la velocidad de muestreo y almacenar los datos para su uso posterior.

Figura\(\PageIndex{9}\): El ADC0844. Reimpreso cortesía de Texas Instrutments

Figura\(\PageIndex{10}\): Diagrama de tiempos para el ADC0844. Reimpreso cortesía de Texas Instrutments

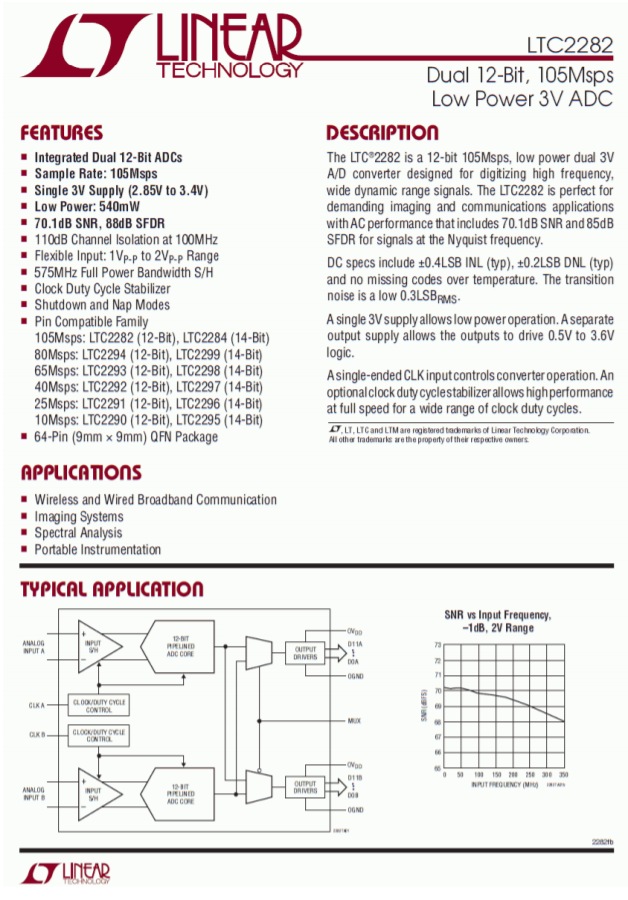

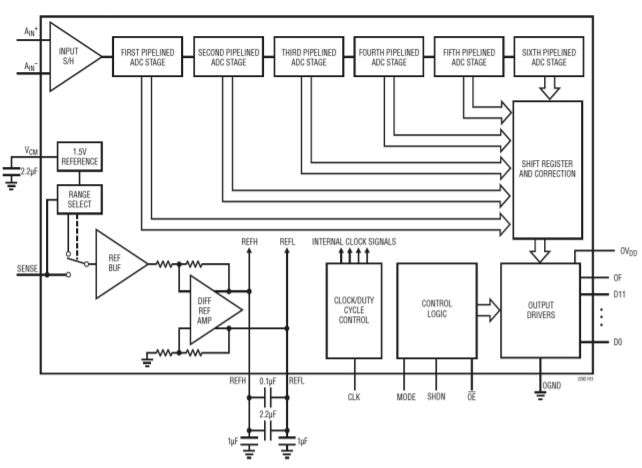

LTC2282

El LTC2282 es un convertidor de 12 bits y 105 mega-muestras por segundo con una muestra y retención interna. Su ficha técnica se muestra en la Figura\(\PageIndex{11}\). Para lograr su combinación de alta frecuencia de muestreo con resolución relativamente alta, el LTC2282 se basa en una técnica conocida como canalización. En este chip en particular, el ducto consta de seis etapas. Cada etapa produce una señal digital de solo tres bits y una señal de error conocida como residual. El residual se pasa a la siguiente etapa donde se multiplica por una ganancia fija, elevándolo así al peso de bits anterior. El residuo recién resultante se pasa a la siguiente etapa donde se repite el proceso. En esencia, la señal se propaga por la tubería de una manera conceptualmente similar a la técnica de aproximación sucesiva. Tenga en cuenta que la canalización acelera el proceso de conversión porque una vez que el residuo pasa a la siguiente etapa, la etapa o etapas anteriores pueden comenzar a trabajar en las siguientes muestras.

Figura\(\PageIndex{11a}\): LTC2282. Reimpreso cortesía de Linear Technology

Figura\(\PageIndex{11b}\): Diagrama de bloques LTC2282. Reimpreso cortesía de Linear Technology

El LTC2282 se utiliza para aplicaciones que requieren tanto alta velocidad como alta resolución. También ofrece autocalibración, operación de fuente de alimentación única de +5 V y bajo consumo de energía.

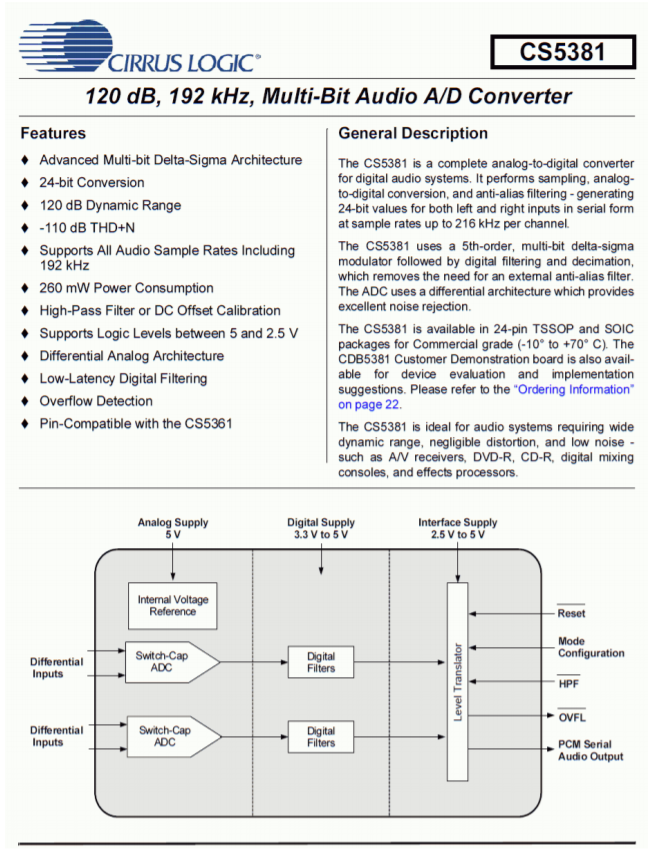

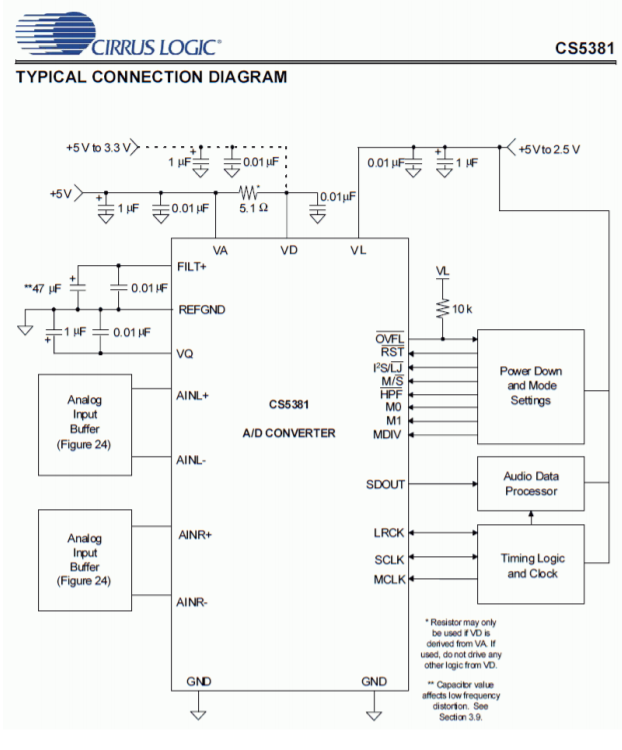

CS5381

El CS5381 ofrece una resolución estéreo de 24 bits con una frecuencia de muestreo máxima de 192 kHz. Esto es ideal para una amplia gama de sistemas de audio digital de alta calidad. Las hojas de datos CS5381 se muestran en la Figura\(\PageIndex{12}\). Este IC utiliza la técnica de conversión delta-sigma y logra un rango dinámico de 120 dB. La clasificación de señal a ruido más distorsión (THD+N) suele ser de 110 dB. El dispositivo sobremuestrea la entrada a 6.144 MHz y tiene configuraciones lógicas para tasas de conversión efectivas 1X, 2X y 4X en su salida. Por ejemplo, la frecuencia de muestreo estándar pro-audio es de 48 kHz con doble frecuencia a 96 kHz y frecuencia cuádruple a 192 kHz.

Al igual que con cualquier convertidor de alta resolución, debe tener especial cuidado con el diseño del circuito o puede resultar un ruido excesivo. Se debe prestar atención a la derivación adecuada de la fuente de alimentación. El CS5381, como muchos CI en esta categoría, requiere fuentes de alimentación analógicas y digitales separadas. Aunque este IC solo requiere 5 V, tenga en cuenta que existen conexiones físicas separadas para alimentación analógica y digital. Los suministros lógicos estándar suelen ser demasiado ruidosos para su uso en tales dispositivos de precisión y degradarán el rendimiento general de audio cuando se aplican a la porción analógica del IC.

Figura\(\PageIndex{12a}\): CS5381. Reimpreso cortesía de Cirrus Logic, Inc.

Figura\(\PageIndex{12b}\): Diagrama de conexión CS5381. Reimpreso cortesía de Cirrus Logic, Inc.

12.5.3: Aplicaciones de Circuitos Integrados Convertidores Analógico-Digital

Ejemplo\(\PageIndex{1}\)

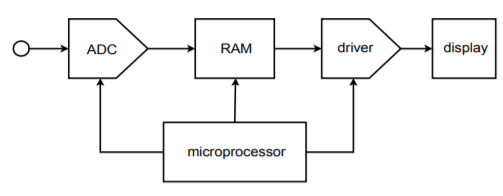

Quizás la aplicación más directa de la conversión analógico-digital es la adquisición de una señal. Una vez en el dominio digital, la señal puede procesarse de diversas maneras. Un ejemplo de ello es el Osciloscopio Digital Sampling (DSO). Un diagrama de bloques simplificado de un DSO se muestra en la Figura\(\PageIndex{13}\). Dado que la salida final del sistema es un gráfico simple, generalmente no tiene sentido resolver la entrada más allá de los 8 bits (256 pasos), y a menudo se pueden usar incluso menos bits. Por lo general, las altas tasas de muestreo son más importantes que la resolución fina en esta aplicación. En consecuencia, los convertidores de 12 y 16 bits no se encuentran aquí. En cambio, se utilizan convertidores de baja resolución capaces de muestrear a cientos de MHz.

Figura\(\PageIndex{13}\): Osciloscopio básico de muestreo digital.

Los DSO generalmente se pueden ejecutar en uno de dos modos: continuo o de disparo único. En modo de disparo único, el ADC adquiere la señal y la almacena en la memoria. Estos datos pueden entonces ser enrutados a los circuitos de visualización continuamente con el fin de crear una traza en la pantalla. La señal es capturada y almacenada en la memoria de la computadora, por lo que se puede reproducir prácticamente para siempre sin pérdida de claridad. Esto es muy útil para atrapar transitorios rápidos y no repetitivos. Una vez capturada la señal, puede examinarse en el tiempo libre. Para el caso, si se incluye alguna forma de lógica de detección de nivel, el muestreo puede iniciarse por eventos transitorios específicos. Esto se conoce como canguro. Por ejemplo, podría sospechar que un circuito que ha diseñado ocasionalmente emite un pico de voltaje indeseable. No es práctico para ti conectar el circuito y mirar la cara de un osciloscopio, quizás por horas, esperando que el sistema se porte mal. En su lugar, el DSO puede programarse para esperar el evento transitorio antes de grabar. De esta manera, podrás dejar el sistema, y cuando regreses algún tiempo después, el pico se habrá registrado y estará esperando tu inspección.

Figura\(\PageIndex{14}\): MDO Comercial. Derechos de autor © Tektronix. Reimpreso con permiso. Todos los derechos reservados

Una extensión de este concepto es la grabación previa al disparador. En esta variación, el DSO está constantemente grabando y “desechando” datos. Cuando finalmente ocurre el pico transitorio, el DSO tiene una instantánea de los eventos que conducen al pico, así como el pico en sí. Esto puede proporcionar información muy útil en algunas aplicaciones. En cualquier caso, dado que los datos están en forma digital, pueden ser descargados a una computadora para su posterior análisis. De hecho, muchos DSO ofrecen algunas funciones interesantes de análisis a bordo, incluyendo suavizado de señal (reducción de ruido), cursores de traza que permiten un cálculo sencillo de tiempo delta /voltaje delta, funciones matemáticas básicas, cálculo de espectro a través de FFT y más.

En modo continuo, un DSO parece funcionar de la misma manera que un osciloscopio analógico ordinario. En este modo, el DSO muestrear la señal de entrada y pasa los datos a la memoria. A partir de aquí los datos se retransmiten a la circuitería de visualización donde se produce una traza. El rastro se actualiza constantemente, por lo que cualquier cambio en la entrada se mostrará rápidamente.

El concepto básico del DSO se ha ampliado al MSO y al MDO. El MSO, o osciloscopio de señal mixta, agrega mediciones de dominio digital mientras que el MDO, u osciloscopio de dominio mixto, extiende el MSO al dominio de frecuencia también.

Ejemplo\(\PageIndex{2}\)

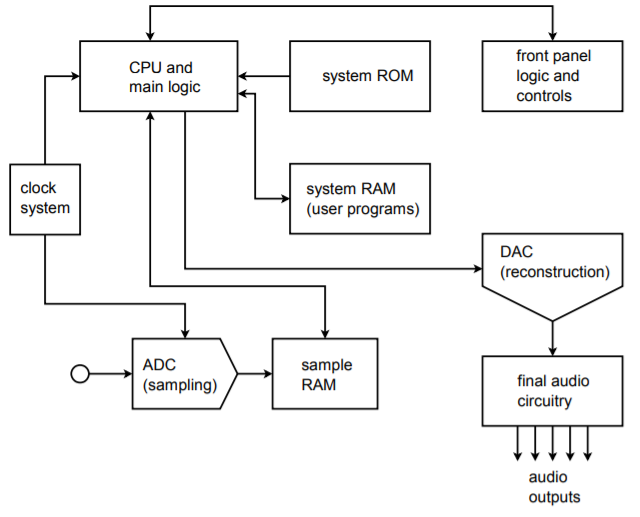

Otra aplicación interesante del convertidor analógico a digital es en el teclado de música de muestreo digital o computadora de batería (generalmente denominado sampler). El uso de un muestreador es bastante sencillo, en realidad. La idea es imitar el sonido de un determinado instrumento (como una trompeta o una flauta) desde el teclado. Antes de la llegada del sampler, esto se hacía ajustando correctamente los filtros, amplificadores y osciladores de un sintetizador de teclado. Aunque los sonidos resultantes estaban razonablemente cerca del instrumento deseado, generalmente no estaban lo suficientemente cerca como para engañar al oyente promedio. El muestreador evita los problemas de los sintetizadores al grabar directamente un instrumento con un convertidor analógico-digital. Por ejemplo, un trompetista podría sonar\(A\) en un micrófono que está conectado al sampler. Esta nota es digitalizada y almacenada en RAM. Ahora, cuando el tecladista golpea la\(A\) tecla, los datos se recuperan de la RAM y se alimentan a un DAC donde se reconstruye. El resultado es exactamente la misma nota que originalmente produjo el trompetista. Al grabar varios tonos diferentes de muchos instrumentos diferentes, el teclista literalmente tiene el poder de toda una orquesta al alcance de su mano. Por supuesto, no hay límite para los sonidos que podrían ser muestreados, y el teclista podría usar el sampler con la misma facilidad para “tocar” una colección de ladridos de perros, golpes de puerta y llamadas de pájaros. Una computadora de batería de muestreo es similar a un teclado de muestreo, pero reemplaza el teclado musical estándar con una serie de botones que permiten al músico crear una secuencia programada de notas. Esta secuencia se puede reproducir en cualquier momento, y prácticamente a cualquier tempo. De esta manera, se puede simular una sección de percusión completa utilizando grabaciones digitales de tambores reales. En la Figura se muestra un diagrama de bloques de un sistema típico de muestreo musical\(\PageIndex{15}\).

Figura\(\PageIndex{15}\): Diagrama de bloques del dispositivo de muestreo y reproducción de instrumentos musicales.

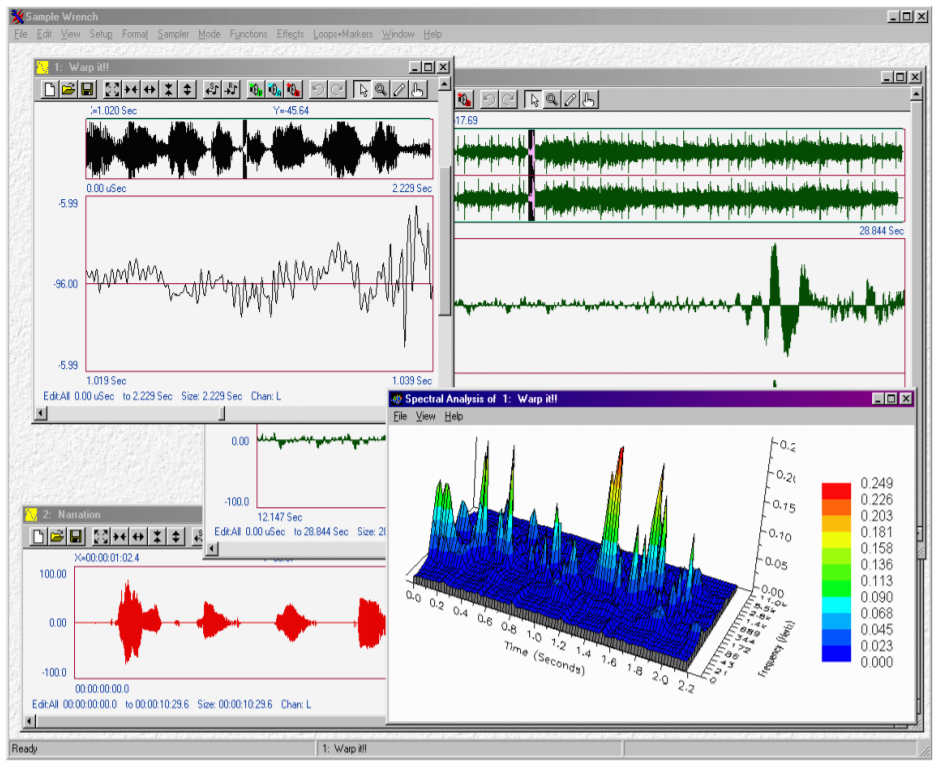

Otras mejoras en el instrumento musical de muestreo digital incluyen conexiones directas a computadoras personales. De esta manera, la computadora puede ser utilizada para analizar y aumentar las muestras de sonido de nuevas formas. Por ejemplo, la computadora personal puede usarse para crear una visualización gráfica de la forma de onda, o calcular y mostrar los componentes espectrales del sonido usando una técnica popular llamada Transformada Rápida de Fourier. Un ejemplo se muestra en la Figura\(\PageIndex{16}\). Por último, la computadora puede programarse para “reproducir” el muestreador. De esta manera, incluso los no teclistas pueden aprovechar la flexibilidad musical inherente que ofrece este sistema.

Figura\(\PageIndex{16}\): Software comercial de visualización y edición de formas de onda. Reimpreso cortesía de disidentes