10.5: Cierres activados por los bordes- Chanclas

- Page ID

- 154486

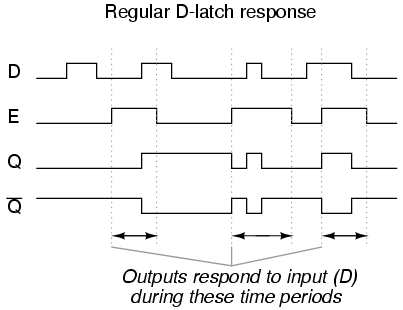

Hasta ahora, hemos estudiado los circuitos de enganche S-R y D con entradas habilitadas. El pestillo responde a las entradas de datos (S-R o D) solo cuando se activa la entrada de habilitación. En muchas aplicaciones digitales, sin embargo, es deseable limitar la capacidad de respuesta de un circuito de enganche a un periodo de tiempo muy corto en lugar de la duración completa en la que se activa la entrada de activación. Un método para habilitar un circuito multivibrador se llama disparo de borde, donde las entradas de datos del circuito tienen control solo durante el tiempo en que la entrada de habilitación está pasando de un estado a otro. Comparemos los diagramas de tiempo para un pestillo D normal frente a uno que está activado por el borde:

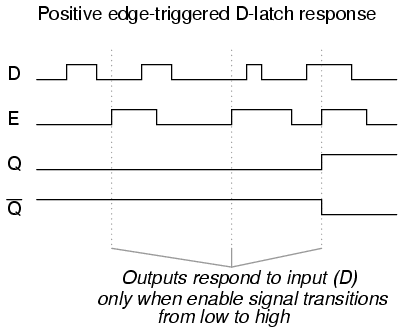

En el primer diagrama de tiempos, las salidas responden a la entrada D siempre que la entrada enable (E) es alta, por mucho tiempo que permanezca alta. Cuando la señal de activación vuelve a un estado bajo, el circuito permanece enganchado. En el segundo diagrama de tiempos, observamos una respuesta claramente diferente en las salidas del circuito: solo responde a la entrada D durante ese breve momento de tiempo cuando la señal de habilitación cambia, o transita, de baja a alta. Esto se conoce como desencadenante de borde positivo.

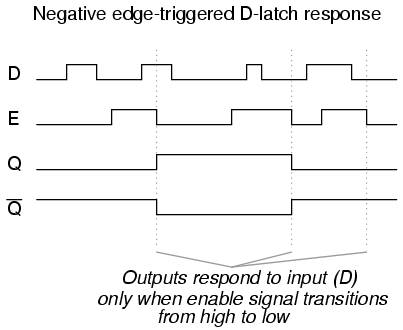

También existe la activación de borde negativo, y produce la siguiente respuesta a las mismas señales de entrada:

Siempre que habilitamos un circuito multivibrador en el borde de transición de una señal de habilitación de onda cuadrada, lo llamamos flip-flop en lugar de un pestillo. En consecuencia, y el circuito S-R activado por el borde se conoce más correctamente como un biestable S-R, y un circuito D activado por el borde como un biestable D. La señal de activación se renombra para que sea la señal de reloj. También, nos referimos a las entradas de datos (S, R y D, respectivamente) de estos flip-flops como entradas sincrónicas, ya que solo tienen efecto en el momento del borde del pulso de reloj (transición), sincronizando así cualquier cambio de salida con ese pulso de reloj, en lugar de al capricho de las entradas de datos.

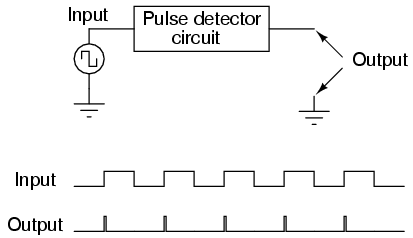

Pero, ¿cómo logramos realmente este desencadenamiento de bordes? Crear un pestillo S-R “cerrado” a partir de un pestillo S-R regular es bastante fácil con un par de puertas AND, pero ¿cómo implementamos una lógica que solo presta atención al borde ascendente o descendente de una señal digital cambiante? Lo que necesitamos es un circuito digital que emita un breve pulso cada vez que la entrada se activa por un periodo de tiempo arbitrario, y podamos usar la salida de este circuito para habilitar brevemente el pestillo. Aquí nos estamos adelantando un poco, pero esto en realidad es una especie de multivibrador monoestable, al que por ahora llamaremos detector de pulsos.

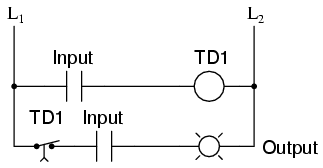

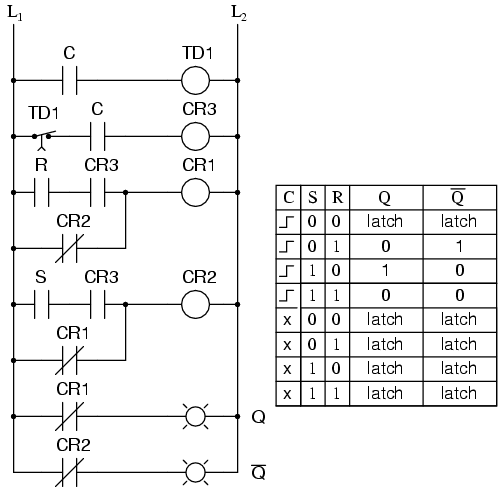

La duración de cada pulso de salida es establecida por componentes en el propio circuito de pulsos. En la lógica de escalera, esto se puede lograr con bastante facilidad mediante el uso de un relé de retardo de tiempo con un tiempo de retardo muy corto:

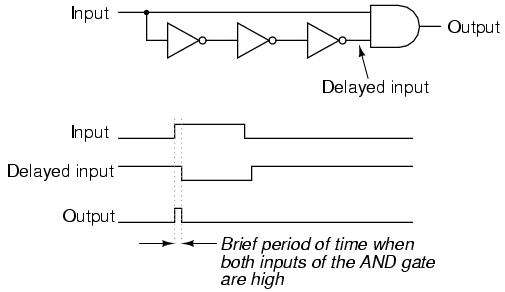

Implementar esta función de temporización con componentes semiconductores es realmente bastante fácil, ya que explota el retardo de tiempo inherente dentro de cada puerta lógica (conocida como retardo de propagación). Lo que hacemos es tomar una señal de entrada y dividirla de dos maneras, luego colocar una puerta o una serie de puertas en una de esas rutas de señal solo para retrasarla un poco, luego hacer que tanto la señal original como su contraparte retardada entren en una puerta de dos entradas que emite una señal alta por el breve momento de tiempo que el la señal retardada aún no ha alcanzado el cambio de bajo a alto en la señal no retardada. Un circuito de ejemplo para producir un pulso de reloj en una transición de señal de entrada de baja a alta se muestra aquí:

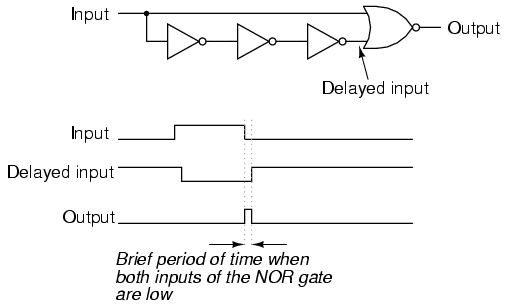

Este circuito se puede convertir en un circuito detector de impulsos de borde negativo con solo un cambio de la puerta final de AND a NOR:

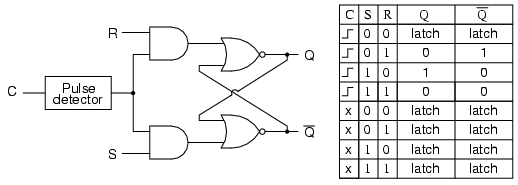

Ahora que sabemos cómo se puede hacer un detector de pulsos, podemos mostrarlo unido a la entrada de habilitación de un pestillo para convertirlo en un flip-flop. En este caso, el circuito es un flip-flop S-R:

Solo cuando la señal de reloj (C) está en transición de baja a alta, el circuito responde a las entradas S y R. Para cualquier otra condición de la señal de reloj (“x”) el circuito se bloqueará.

Aquí se muestra una versión lógica de escalera del flip-flop S-R:

El contacto de relé CR 3 en el diagrama de escalera toma el lugar del contacto E antiguo en el circuito de cierre S-R y se cierra solo durante el corto tiempo que tanto C está cerrado como el contacto de retardo TR 1 está cerrado. En cualquier caso (circuito de puerta o escalera), vemos que las entradas S y R no tienen ningún efecto a menos que C esté pasando de un estado bajo (0) a un estado alto (1). De lo contrario, las salidas del flip-flop se enganchan en sus estados anteriores.

Es importante tener en cuenta que el estado no válido para el biestable S-R se mantiene solo por el corto período de tiempo que el circuito detector de pulsos permite que se habilite el pestillo. Después de que haya transcurrido ese breve período de tiempo, las salidas se engancharán en el estado establecido o en el estado de reinicio. Una vez más, el problema de una condición racial se manifiesta. Sin señal de activación, no se puede mantener un estado de salida no válido. Sin embargo, los estados válidos “enganchados” del multivibrador—set y reset—son mutuamente excluyentes entre sí. Por lo tanto, las dos puertas del circuito multivibrador se “correrán” entre sí por la supremacía, y cualquiera que alcance primero un estado de alto rendimiento “ganará”.

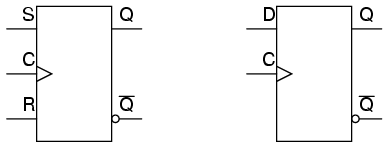

Los símbolos de bloque para las chanclas son ligeramente diferentes de los de sus respectivas contrapartes de pestillo:

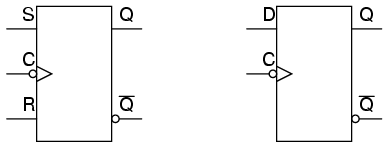

El símbolo del triángulo junto a las entradas del reloj nos dice que estos son dispositivos activados por los bordes, y en consecuencia que estos son flip-flops en lugar de pestillos. Los símbolos anteriores son activados por el borde positivo: es decir, “registran” en el borde ascendente (transición de baja a alta) de la señal de reloj. Los dispositivos activados por el borde negativo se simbolizan con una burbuja en la línea de entrada del reloj:

Ambos flip-flops anteriores “sincronizarán” en el borde descendente (transición de alto a bajo) de la señal de reloj.

Revisar

- Un flip-flop es un circuito de cierre con un circuito de “detector de pulsos” conectado a la entrada enable (E), de modo que se habilita solo por un breve momento ya sea en el borde ascendente o descendente de un pulso de reloj.

- Los circuitos detectores de pulsos pueden estar hechos de relés de retardo de tiempo para aplicaciones lógicas de escalera, o de puertas semiconductoras (explotando el fenómeno del retardo de propagación).