10.7: Entradas flip-flop asíncronas

- Page ID

- 154485

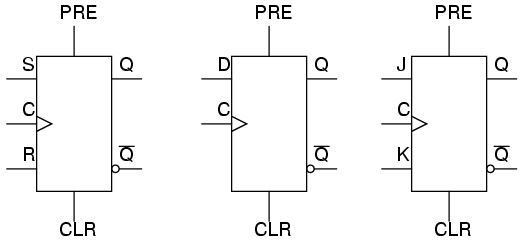

Las entradas de datos normales a un flip flop (D, S y R, o J y K) se denominan entradas síncronas porque tienen efecto sobre las salidas (Q y no-Q) solo en paso, o en sincronía, con las transiciones de señal de reloj. Estas entradas extra que ahora traigo a su atención se llaman asíncronas porque pueden configurar o restablecer el flip-flop independientemente del estado de la señal del reloj. Por lo general, se llaman preestablecidos y claros:

Cuando se activa la entrada preestablecida, el flip-flop se establecerá (Q=1, not-Q=0) independientemente de cualquiera de las entradas síncronas o del reloj. Cuando se activa la entrada clara, el flip-flop se restablecerá (Q=0, not-Q=1), independientemente de cualquiera de las entradas síncronas o del reloj. Entonces, ¿qué sucede si se activan tanto las entradas preestablecidas como las claras? Sorpresa, sorpresa: obtenemos un estado no válido en la salida, donde Q y no-Q van al mismo estado, lo mismo que nuestro viejo amigo, ¡el pestillo S-R! Las entradas predefinidas y claras encuentran uso cuando se agrupan múltiples flip-flops para realizar una función en una palabra binaria de varios bits, y se necesita una sola línea para establecerlos o restablecerlos todos a la vez.

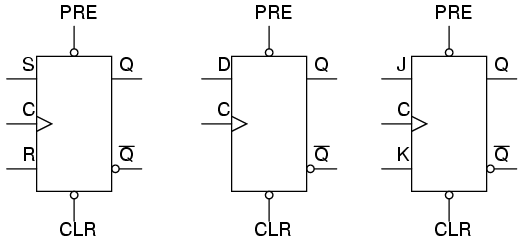

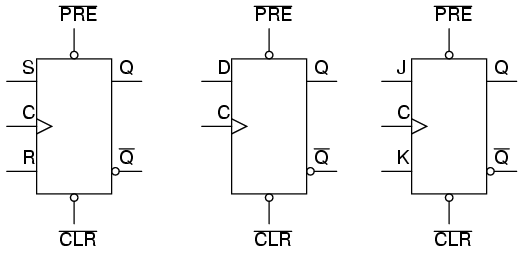

Las entradas asincrónicas, al igual que las entradas síncronas, pueden diseñarse para que sean activas-altas o activas-bajas. Si están activo-bajo, habrá una burbuja inversora en ese cable de entrada en el símbolo de bloque, al igual que las entradas de reloj de activación de borde negativo.

A veces las designaciones “PRE” y “CLR” se mostrarán con barras de inversión por encima de ellas, para denotar aún más la lógica negativa de estas entradas:

Revisar

- Las entradas asincrónicas en un flip-flop tienen control sobre las salidas (Q y no-Q) independientemente del estado de entrada del reloj.

- Estas entradas se denominan preset (PRE) y clear (CLR). La entrada preestablecida conduce el flip-flop a un estado establecido mientras que la entrada de borrar lo conduce a un estado de reinicio.

- Es posible conducir las salidas de un flip-flop J-K a una condición no válida usando las entradas asíncronas, ya que toda la retroalimentación dentro del circuito multivibrador es anulada.