15.3: Memoria no mecánica moderna

- Page ID

- 154508

Ahora podemos proceder a estudiar tipos específicos de dispositivos de almacenamiento digital. Para comenzar, quiero explorar algunas de las tecnologías que no requieren ninguna pieza móvil. Estas no son necesariamente las tecnologías más nuevas, como se podría sospechar, aunque lo más probable es que reemplacen a las tecnologías de partes móviles en el futuro.

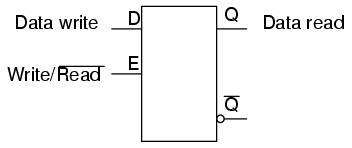

Un tipo muy sencillo de memoria electrónica es el multivibrador biestable. Capaz de almacenar un solo bit de datos, es volátil (requiere energía para mantener su memoria) y muy rápido. El D-latch es probablemente la implementación más simple de un multivibrador biestable para uso de memoria, la entrada D que sirve como entrada de “escritura” de datos, la salida Q que sirve como salida de “lectura” y la entrada de habilitación que sirve como línea de control de lectura/escritura:

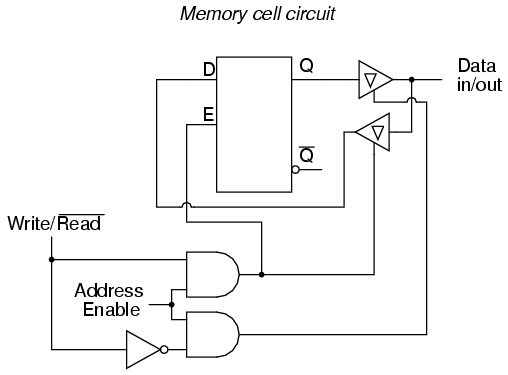

Si deseamos más de un bit de almacenamiento (y probablemente lo hagamos), tendremos que tener muchos pestillos dispuestos en algún tipo de matriz donde podamos abordar selectivamente cuál (o qué conjunto) estamos leyendo o escribiendo. Usando un par de búferes triestatales, podemos conectar tanto la entrada de escritura de datos como la salida de lectura de datos a una línea de bus de datos común, y habilitar esos búferes para conectar la salida Q a la línea de datos (READ), conectar la entrada D a la línea de datos (WRITE), o mantener ambos búferes en el estado High-Z para desconectar D y Q de la línea de datos (modo no direccionado). Una “celda” de memoria se vería así, internamente:

Cuando la entrada de habilitación de dirección es 0, ambos búferes triestados se colocarán en modo Z alto, y el pestillo se desconectará de la línea de entrada/salida de datos (bus). Solo cuando la entrada de habilitación de dirección esté activa (1) se conectará el pestillo al bus de datos. Cada circuito de enganche, por supuesto, se habilitará con una línea de entrada diferente de “habilitación de dirección” (AE), que vendrá de un decodificador de salida 1-de-n:

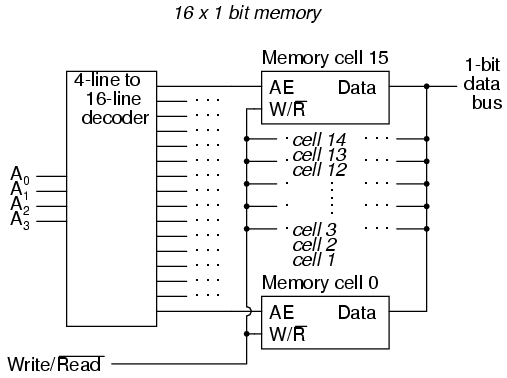

En el circuito anterior, 16 celdas de memoria son direccionadas individualmente con una entrada de código binario de 4 bits en el decodificador. Si no se direcciona una celda, se desconectará del bus de datos de 1 bit por sus búferes triestatales internos: en consecuencia, los datos no pueden escribirse ni leerse a través del bus hacia o desde esa celda. Solo el circuito celular que es direccionado por la entrada del decodificador de 4 bits será accesible a través del bus de datos.

Este sencillo circuito de memoria es de acceso aleatorio y volátil. Técnicamente, se le conoce como RAM estática. Su capacidad total de memoria es de 16 bits. Dado que contiene 16 direcciones y tiene un bus de datos de 1 bit de ancho, se designaría como un circuito RAM estático de 16 x 1 bit. Como puede ver, se necesita una increíble cantidad de puertas (¡y múltiples transistores por puerta!) para construir un circuito práctico de RAM estática. Esto hace que la RAM estática sea un dispositivo de densidad relativamente baja, con menos capacidad que la mayoría de los otros tipos de tecnología de RAM por unidad de espacio de chip IC. Debido a que cada circuito de celda consume una cierta cantidad de energía, el consumo general de energía para una gran matriz de celdas puede ser bastante alto. Los primeros bancos de RAM estáticos en las computadoras personales consumían una buena cantidad de energía y también generaban mucho calor. La tecnología CMOS IC ha permitido reducir el consumo específico de energía de los circuitos de RAM estáticos, pero la baja densidad de almacenamiento sigue siendo un problema.

Para abordar esto, los ingenieros recurrieron al condensador en lugar del multivibrador biestable como medio para almacenar datos binarios. Un pequeño condensador podría servir como celda de memoria, completo con un solo transistor MOSFET para conectarlo al bus de datos para cargar (escribir un 1), descargar (escribir un 0) o leer. Desafortunadamente, esos condensadores diminutos tienen capacitancias muy pequeñas, y su carga tiende a “filtrarse” a través de cualquier impedancia de circuito con bastante rapidez. Para combatir esta tendencia, los ingenieros diseñaron circuitos internos al chip de memoria RAM que leerían periódicamente todas las celdas y recargarían (o “refrescarían”) los condensadores según fuera necesario. Si bien esto se sumó a la complejidad del circuito, aún requirió muchos menos componentes que una RAM construida con multivibradores. Llamaron a este tipo de circuito de memoria RAM dinámica, por su necesidad de refrescarse periódicamente.

Los recientes avances en la fabricación de chips CI han llevado a la introducción de la memoria flash, que funciona según un principio de almacenamiento capacitivo como la RAM dinámica, pero utiliza la puerta aislada de un MOSFET como el propio condensador.

Antes de la llegada de los transistores (especialmente el MOSFET), los ingenieros tenían que implementar circuitos digitales con puertas construidas a partir de tubos de vacío. Como se puede imaginar, el enorme tamaño comparativo y el consumo de energía de un tubo de vacío en comparación con un transistor hicieron que los circuitos de memoria como la RAM estática y dinámica fueran una imposibilidad práctica. Se desarrollaron otras técnicas, bastante ingeniosas, para almacenar datos digitales sin el uso de partes móviles.