5.5: Mejora transitoria y en estado estacionario

- Page ID

- 84920

Diseños de plomo-retraso y PID

Cuando las especificaciones de diseño del sistema de control requieren una mejora simultánea de la respuesta transitoria y el error de seguimiento en estado estacionario, se puede considerar un lead lag o un controlador PID.

Un controlador lead-lag combina las etapas phase lead y phase lag; como regla general, la respuesta transitoria se mejora primero, seguida de la mejora del error de estado estacionario. El controlador de lead lag se expresa como:

\[K(s)=K\left(\frac{s+z_{\rm c1}}{s+p_{\rm c1}}\right)\left(\frac{s+z_{\rm c2}}{s+p_{\rm c2}}\right),\quad z_{\rm c1}<p_{\rm c1}, \; z_{\rm c2}>p_{\rm c2}\]

un controlador PID combina de manera similar controladores PD y PI. Se expresa como:

\[K(s)=K\left({s+z_{\rm c1}}\right)\left(\frac{s+z_{\rm c2}}{s}\right) \]

Como regla general, la mejora de la respuesta transitoria se dirige primero. El polo y el cero seleccionados para el diseño de plomo de fase o PD dirigen el lugar de la raíz hacia las ubicaciones de polo de bucle cerrado deseadas. El par polo-cero en la parte de fase-lag o PI del diseño se ubica cerca del origen para perturbar mínimamente el locus radicular existente.

Diseño Lead-Lag

Ejemplo\(\PageIndex{1}\): Lead-Lag Design

Dejar\(G\left(s\right)=\frac{10}{s\left(s+2\right)(s+5)}\); asumir que las especificaciones de diseño son:\(\% {\rm O}S\le 10\% ,\; \; t_\rm s \le 2\rm s,\; \; e_{\rm ss} |_{{\rm r}amp} \le 0.1.\) Estas especificaciones se traducen en:\(\zeta \ge 0.6,\ \sigma \ge 2,\ K_v\ge 10\).

Diseño de Plomo de Fase. El diseño del controlador de cable de fase (cubierto en el Ejemplo 5.3.3) procede de la siguiente manera: Let\(s_1=-2.2\pm j2.4,\;\;\zeta =0.68,\) denotar una ubicación de polo de bucle cerrado deseada; entonces\(G\left(s_1\right)=0.35\angle 92{}^\circ\), es decir, la contribución de fase del controlador requerida es:\(K\left(s_1\right)=K\angle 88{}^\circ\).

Vamos\(z_c=2,\ p_c=22\); entonces\(K\left(s_1\right)=0.11\angle 88{}^\circ\). De la gráfica RL,\(K=24\) se selecciona una ganancia de controlador para raíces de bucle cerrado en:\(s=-2.2\pm j2.4\). Por lo tanto, la sección de plomo de fase está diseñada como:\(K_{\rm lead}\left(s\right)=24\left(\frac{s+2}{s+22}\right)\).

Diseño de retardo de fase. Para\(K_{\rm lead} (s)G(s)\), la constante de error de velocidad se da como:\(K_v=2.2\). Para aumentar la constante de error a\(K_v>10\), se considera un controlador de retardo\(K_{\rm lag}=\frac{s+0.01}{s+0.002}\) de fase.

La contribución angular del controlador de retardo de fase es:\(\angle K_{\rm lag}\left(s_1\right)=-0.1{}^\circ\) por lo tanto, las raíces dominantes de bucle cerrado se ven afectadas de manera insignificante.

El controlador lead-lag se forma como:\(K\left(s\right)=25\left(\frac{s+2}{s+24}\right)\left(\frac{s+0.01}{s+0.002}\right)\).

La función de transferencia de bucle cerrado se obtiene como:\(T\left(s\right)=\frac{240\left(s+0.01\right)}{\left(s+0.01004\right)\left(s+22.6\right)\left(s^2+4.39s+10.58\right)}\). Las raíces dominantes de bucle cerrado se encuentran en:\(s=-2.2\pm j2.4\ (\zeta =0.68)\).

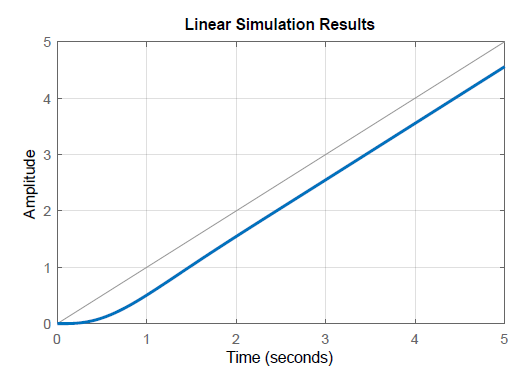

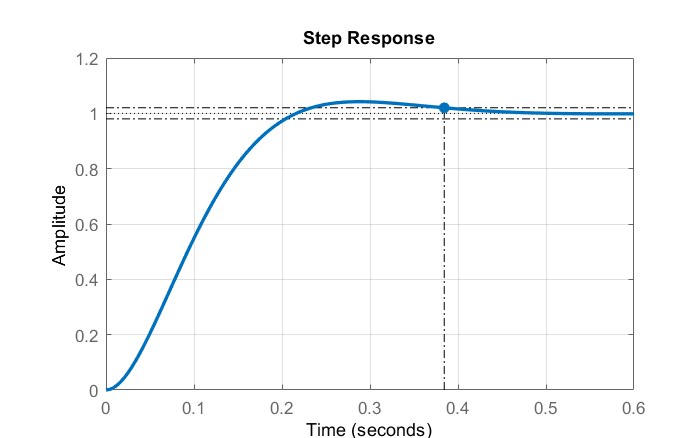

Las respuestas de paso y rampa del sistema de bucle cerrado se representan a continuación. La respuesta de paso muestra un tiempo de establecimiento de\(1.9sec\).

Diseño PID

En el siguiente ejemplo se realiza un diseño de PID alternativo.

Ejemplo\(\PageIndex{2}\): PID Design

Dejar\(G\left(s\right)=\frac{10}{s\left(s+2\right)(s+5)}\); asumir que las especificaciones de diseño son:\(\% {\rm O}S\le 10\% ,\; \; t_\rm s \le 2\rm s,\; \; e_{\rm ss} |_{{\rm r}amp} \le 0.1.\) Estas especificaciones se traducen en:\(\zeta \ge 0.6,\ \sigma \ge 2,\ K_v\ge 10\).

Diseño PD. El controlador PD se da como:\(K_{PD}\left(s\right)=K\left(s+z_c\right)\). Podemos elegir arbitrariamente el controlador cero en\(z_c=-2\), y usar el locus raíz del sistema compensado para seleccionar\(K=1\) con raíces de bucle cerrado en:\(s_1=-2.5\pm j1.95\).

Diseño de PI. El controlador PI se da como:\(\frac{s+z_c}{s}\), donde\(z_c\ll s_1\) se desee. Podemos seleccionar arbitrariamente una ubicación cero:\(z_c=0.01\) para definir el controlador PID como:\(K_{PID}\left(s\right)=\frac{(s+0.01)(s+2)}{s}\).

La función de transferencia de bucle cerrado se da como:\(T\left(s\right)=\frac{10\left(s+0.01\right)}{\left(s+0.01005\right)\left(s+2\right)\left(s^2+4.99s+9.95\right)}\).

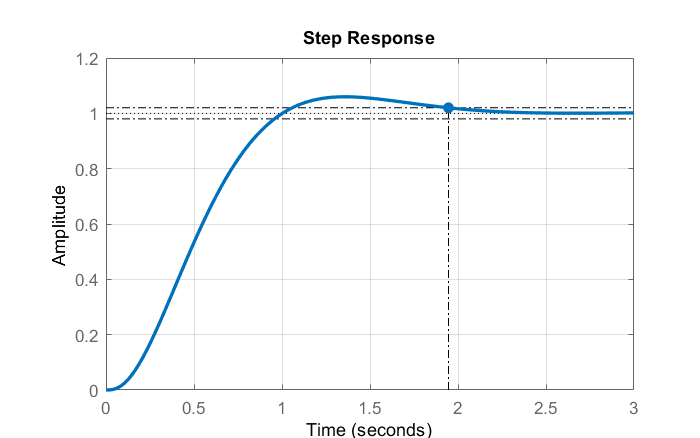

La respuesta escalonada del sistema de bucle cerrado muestra un tiempo de asentamiento de\(t_s=1.8sec\).

Plomo de fase con PI

También podemos combinar el diseño del controlador de fase con un controlador PI para definir el controlador compuesto como se muestra a continuación.

Ejemplo\(\PageIndex{3}\): Phase-Lead with PI

Dejar\(G\left(s\right)=\frac{10}{s\left(s+2\right)(s+5)}\); asumir que las especificaciones de diseño son:\(\% {\rm O}S\le 10\% ,\; \; t_\rm s \le 2\rm s,\; \; e_{\rm ss} |_{\rm ramp} \le 0.1.\) Estas especificaciones se traducen en:\(\zeta \ge 0.6,\ \sigma \ge 2,\ K_v\ge 10\).

Diseño de Plomo de Fase. Vamos\(s_1=-2.2\pm j2.4\,\;\;\zeta =0.68\); entonces, podemos elegir, como en el Ejemplo 5.5.1 anterior,\(z_c=2,\ p_c=22\) y\(K=24\) para raíces de bucle cerrado en:\(s=-2.2\pm j2.4\). El controlador de cable de fase se define como:\(K_{\rm lead}\left(s\right)=24\left(\frac{s+2}{s+22}\right)\).

Diseño de PI. El controlador PI se da como:\(\frac{s+z_c}{s}\). En este caso,\(z_c=0.01\) no parece ser una buena opción, ya que el modo lento en la respuesta de paso sigue siendo dominante, aumentando el tiempo de asentamiento.

Una mejor estrategia es seleccionar el controlador PI cero para cancelar el segundo polo de la planta en\(s=-5\). El controlador compuesto se forma como:\(K\left(s\right)=24\left(\frac{s+2}{s+22}\right)\left(\frac{s+5}{s}\right)\).

La función de transferencia de bucle cerrado resultante después de cancelaciones polo-cero se da como:\(T\left(s\right)=\frac{240}{\left(s^2+22s+240\right)}\), que tiene raíces dominantes de bucle cerrado ubicadas en:\(s=-11\pm j11\ (\zeta =0.7)\).

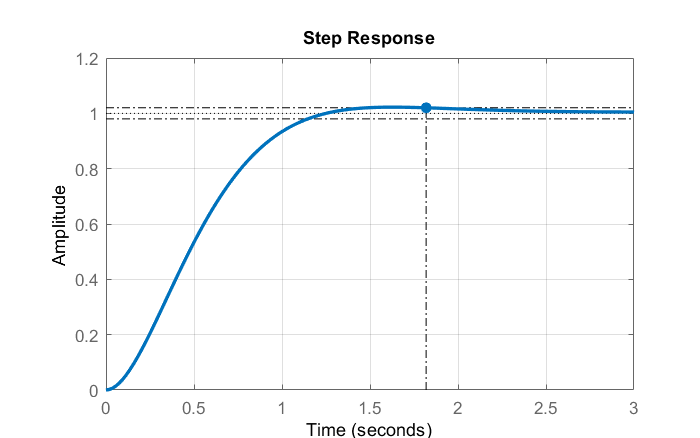

La respuesta escalonada del sistema de bucle cerrado muestra un corto tiempo de asentamiento de\(t_s\cong 0.38sec\).

Sintonización MATLAB del controlador PID

MATLAB Control Systems Toolbox ofrece el comando 'pidtune' para diseñar un controlador PID óptimo o un controlador PID con un filtro para reducir el ruido de alta frecuencia.

Ejemplo\(\PageIndex{4}\): MATLAB PID Controller

Let\(G\left(s\right)=\frac{10}{s\left(s+2\right)(s+5)}\); entonces, el controlador PID sintonizado MATLAB se obtiene como:

\[K\left(s\right)=\frac{2.01\left(s+0.314\right)\left(s+1.43\right)}{s}\]

Las raíces de bucle cerrado resultantes se encuentran en:\(s=-0.34,\ -1.16,\ -2.73\pm 3.71.\)

Alternativamente, el controlador PID sintonizado MATLAB con filtro se obtiene como:

\[K\left(s\right)=\frac{727.25\left(s+0.302\right)\left(s+1.41\right)}{s\left(s+361.4\right)}\]

Las raíces de bucle cerrado resultantes se encuentran en:\(s=-0.34,\ -1.16,\ -2.73\pm 3.71,\ -361.5.\)

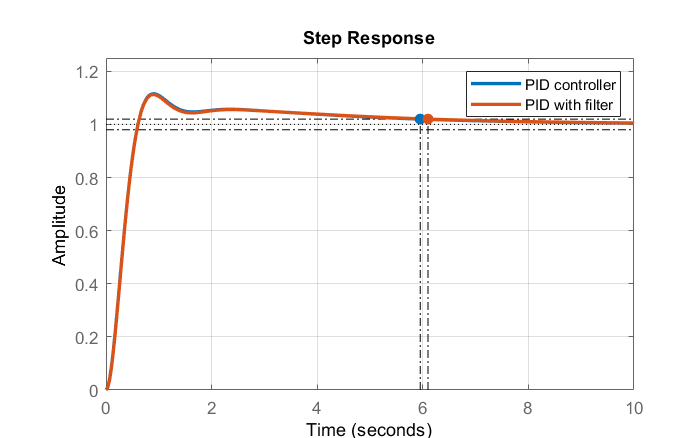

Las respuestas del sistema de bucle cerrado para los controladores PID diseñados por MATLAB se representan a continuación. Las respuestas son casi idénticas con un sobreimpulso de aproximadamente\(10\%\) con un tiempo de asentamiento de\(t_s\cong 6sec\).