7.1: Introducción

- Page ID

- 82892

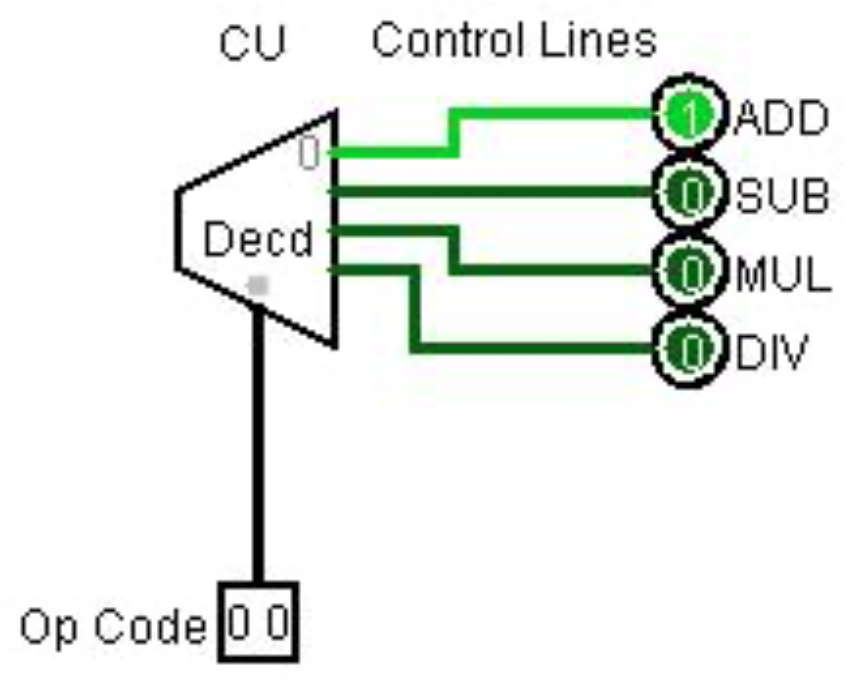

Los decodificadores son circuitos que rompen una entrada de n bits en 2 n líneas de salida individuales. Por ejemplo, un decodificador podría dividir el código de operaciones de 2 bits en 4 operaciones separadas. El código de operación le dice a la CPU qué operaciones ejecutar. Un código de operación de 2 bits se resume en la siguiente tabla. Aquí el código 00 corresponde a la operación ADD, 01 corresponde, a SUB, etc.

|

Código |

Operación |

|

00 |

AGREGAR |

|

01 |

SUB |

|

10 |

MUL |

|

11 |

DIV |

La Unidad de Control (CU) de la CPU rompería el número binario para que cada operación coincidiera exactamente con una línea de control. Esto se llama decodificador de 2 a 4 ya que 2 bits de entrada se convierten en 4 líneas de salida. En la siguiente figura se muestra un esquema del decodificador para implementar esta CU.

La mayoría de las CPU admiten conjuntos de instrucciones que son mucho más grandes que simplemente ADD/SUB/MUL/DIV, y por lo tanto un decodificador de 2 a 4 no es tan común, sin embargo, los principios utilizados para crear un decodificador de 2 a 4 son los mismos incluso cuando el tamaño del decodificador se vuelve más grande. En este capítulo solo se analizará el decodificador de 2 a 4. Los decodificadores de mayor tamaño serán considerados en los ejercicios al final del capítulo.