7.12: Aplicaciones para Películas Delgadas de Sílice

- Page ID

- 69512

Introducción

Si bien las propiedades físicas de la sílice la hacen adecuada para su uso en aplicaciones de recubrimiento protector y óptico, la mayor aplicación de películas delgadas aislantes de SiO 2 es, sin duda, en dispositivos semiconductores, en los que el aislador realiza una serie de tareas específicas, entre ellas: pasivación superficial, capa de puerta de transistor de efecto de campo (FET), capas de aislamiento, planarización y empaque.

El término aislante generalmente se refiere a un material que exhibe baja conductividad térmica o eléctrica; los materiales eléctricamente aislantes también se denominan dieléctricos. Es en lo que respecta a la alta resistencia al flujo de una corriente eléctrica que las películas delgadas de SiO 2 son de la mayor importancia comercial. La constante dieléctrica (ε) es una medida de la capacidad de los materiales dieléctricos para almacenar carga, y se caracteriza por la energía electrostática almacenada por unidad de volumen a través de un gradiente de potencial unitario. La magnitud de ε es una indicación del grado de polarización o desplazamiento de carga dentro de un material. La constante dieléctrica para el aire es 1, y para los sólidos iónicos generalmente está en el rango de 5 - 10. Las constantes dieléctricas se definen como la relación entre la capacitancia del material y la del aire, es decir, (7.12.1). La constante dieléctrica para el dióxido de silicio oscila entre 3.9 y 4.9, para películas cultivadas térmicamente y plasma CVD, respectivamente.

\[ \epsilon \text{ = } \dfrac{\text{C}_{\text{material}}}{\text{C}_{\text{air}}}\]

Una capa aislante es una película o capa depositada de material dieléctrico que separa o cubre capas conductoras. Idealmente, en estas aplicaciones un material aislante debe tener una resistividad superficial mayor a 10 13 Ω/cm 2 o una resistividad volumétrica mayor a 10 11 Ω.cm. Sin embargo, para algunas aplicaciones, son aceptables valores más bajos; generalmente se acepta que un aislante eléctrico tenga una resistividad mayor a 10 5 Ω.cm. Las películas delgadas CVD SiO 2 tienen una resistividad de 10 6 - 10 16 Ω.cm, dependiendo del método de crecimiento de la película.

Como consecuencia de sus propiedades dieléctricas SiO2, y sílices relacionadas, se utilizan para aislar capas conductoras, para facilitar la difusión de dopantes a partir de óxidos dopados, como máscaras de difusión e implantación de iones, tapar películas dopadas para evitar la pérdida de dopante, para absorber impurezas, para protección contra la humedad y la oxidación, y para pasivación electrónica. De los muchos métodos utilizados para la deposición de películas delgadas, la deposición química de vapor (CVD) se usa con mayor frecuencia para el procesamiento de semiconductores. Para apreciar los problemas únicos asociados con el CVD de las películas delgadas aislantes de SiO 2, vale la pena revisar primero algunas de sus aplicaciones. A continuación se resumen tres áreas de mayor importancia para la fabricación de dispositivos semiconductores contemporáneos: aislamiento y aislamiento de puertas, pasivación y planarización.

Aislamiento de dispositivos y aislamiento de compuertas

Un microcircuito puede describirse como una colección de dispositivos cada uno consistente en “un conjunto de componentes activos y pasivos, interconectados dentro de un bloque monolítico de material semiconductor”. Se requiere que cada dispositivo esté aislado de los dispositivos adyacentes para permitir la máxima eficiencia del circuito general. Además, dentro de un dispositivo, los contactos también deben estar aislados eléctricamente. Si bien existen varios métodos para aislar dispositivos individuales dentro de un circuito (uniones polarizadas inversamente, aislamiento de mesa, uso de sustratos semiaislantes y aislamiento de óxido), el aislamiento de los componentes activos en un solo dispositivo se logra casi exclusivamente mediante la deposición de un aislante.

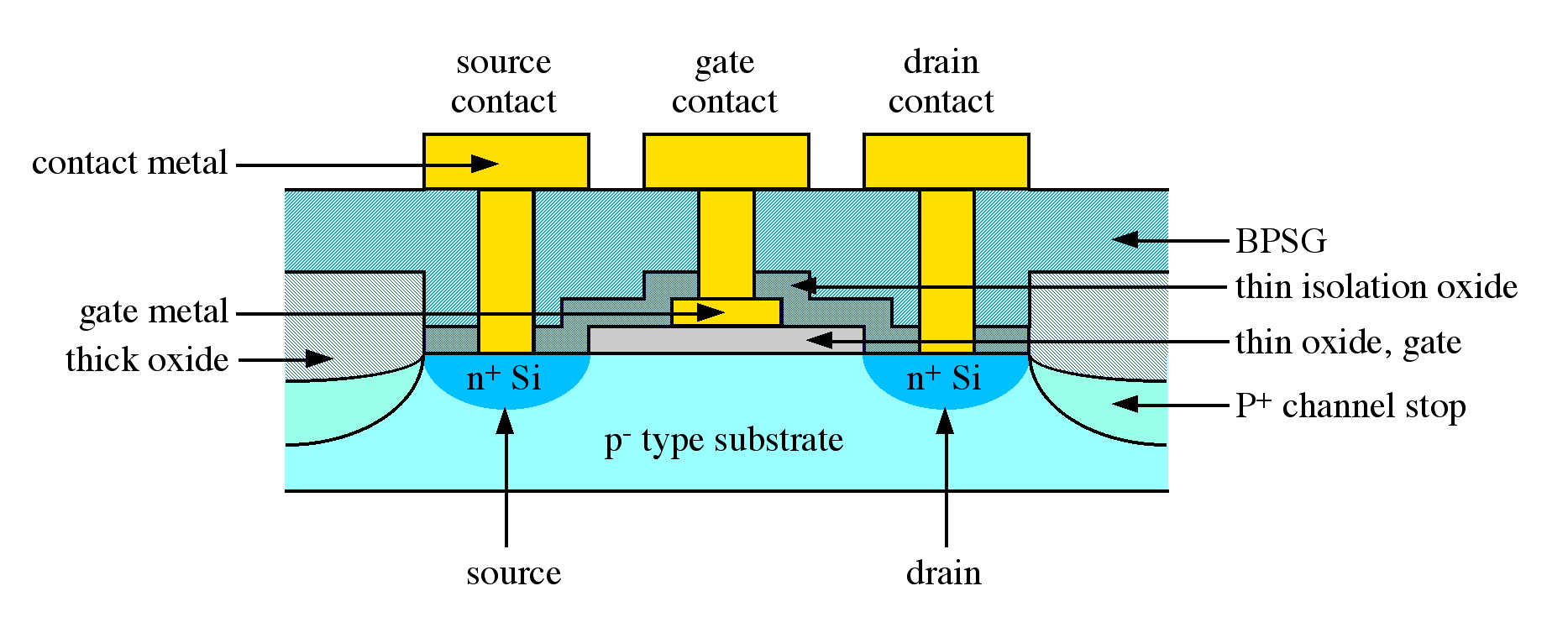

En la Figura se muestra una representación esquemática de un MOSFET de silicio (transistor de efecto de campo metal-óxido-semiconductor). El MOSFET es el componente básico de los circuitos de silicio-CMOS (metal-óxido-semiconductor complementario) que, a su vez, forman la base de circuitos lógicos, como los utilizados en la CPU (unidad central de procesamiento) de una computadora personal moderna. Se puede observar que el MOSFET está aislado de dispositivos adyacentes por una unión con polarización inversa (tope p + -canal) y una gruesa capa de óxido. La puerta, la fuente y el contacto de drenaje están aislados eléctricamente entre sí por un delgado óxido aislante. Un esquema similar se utiliza para el aislamiento del colector tanto de la base como del emisor en dispositivos de transistores bipolares.

Como transistor, un MOSFET tiene muchas ventajas sobre diseños alternativos. La ventaja clave es la baja disipación de energía resultante de la alta impedancia del dispositivo. Esto es resultado de la delgada capa aislante entre el canal (región entre la fuente y el drenaje) y el contacto de la puerta, ver Figura\(\PageIndex{1}\). La presencia de una puerta aislante es característica de una clase general de dispositivos llamados MISFET (transistor de efecto de campo metal-aislador-semiconductor). Los MOSFET son un subconjunto de MISFET donde el aislante es específicamente un óxido, por ejemplo, en el caso de un dispositivo MISFET de silicio el aislante es SiO 2, de ahí MOSFET. Es la fabricación de circuitos MOSFET lo que ha permitido que la tecnología de silicio domine la electrónica digital (circuitos lógicos). Sin embargo, los aumentos en la potencia y velocidad de computación requieren una reducción constante en el tamaño del dispositivo y una mayor complejidad en la arquitectura del dispositivo.

Pasivación

La pasivación a menudo se define como un proceso mediante el cual una película se cultiva en la superficie de un semiconductor para (a) protegerla químicamente del ambiente, o (b) proporcionar estabilización electrónica de la superficie.

Desde los primeros días de la electrónica de estado sólido se ha reconocido que la presencia o ausencia de estados superficiales juega un papel decisivo en la utilidad de cualquier material semiconductor. En la superficie de cualquier material en estado sólido hay sitios en los que el ambiente de coordinación de los átomos es incompleto. Estos sitios, comúnmente denominados “enlaces colgados”, son la causa de los estados electrónicamente activos que permiten la recombinación de agujeros y electrones. Esta recombinación ocurre a energías por debajo del valor aparente, e interfiere con las propiedades inherentes del semiconductor. Para optimizar las propiedades de un dispositivo semiconductor es deseable satisfacer covalentemente todos estos enlaces superficiales, desplazando así los estados superficiales fuera de la banda prohibida y hacia las bandas de valencia o conducción. Por lo tanto, la pasivación electrónica puede describirse como un proceso que reduce la densidad de estados electrónicos disponibles presentes en la superficie de un semiconductor, limitando así las posibilidades de recombinación de agujeros y electrones. En el caso del silicio tanto el óxido nativo como otros óxidos cumplen admirablemente estos requisitos.

La pasivación química requiere un material que inhiba la difusión de oxígeno, agua u otras especies a la superficie del semiconductor subyacente. Además, el material es idealmente duro y resistente al ataque químico. Un material de pasivación perfecto satisfaría los requisitos de pasivación electrónica y química.

Planarización

Para la gran mayoría de los dispositivos electrónicos, el punto de partida es un sustrato que consiste en una oblea plana de cristal único de material semiconductor. Durante el procesamiento, que incluye el crecimiento tanto de películas aislantes como conductoras, la superficie se vuelve cada vez más no plana. Por ejemplo, un óxido de puerta en un MOSFET típico (ver Figura\(\PageIndex{1}\)) puede tener típicamente un espesor de 100 - 250 Å, mientras que el aislamiento o el óxido de campo puede ser de 10,000 Å. Para que la posterior deposición exitosa de capas conductoras (metalización) se produzca sin romper las líneas metálicas (a menudo debido a la dificultad de mantener la cobertura escalonada), la superficie debe ser plana y lisa. Este proceso se llama planarización, y se puede llevar a cabo mediante una técnica conocida como etchback sacrificial. Una etapa abrupta (Figura\(\PageIndex{2}\) a) se recubre con una capa conforme de un dieléctrico de bajo punto de fusión, por ejemplo, vidrio de borofosforosilicato, BPSG (Figura\(\PageIndex{2}\) b), y posteriormente una resina orgánica sacrificial (Figura\(\PageIndex{2}\) c). La muestra es luego grabada por plasma de tal manera que la resina y el dieléctrico se eliminan a la misma velocidad. Dado que el grabado por plasma sigue el contorno de la resina orgánica, se deja atrás una superficie lisa (Figura\(\PageIndex{2}\) d). Por lo tanto, el proceso de planarización reduce significativamente los diferenciales de altura de paso. Además, las regiones o valles entre elementos de metalización individuales (vías) pueden llenarse completamente permitiendo una ruta para producir superficies uniformemente planas, por ejemplo, la película BPSG que se muestra en la Figura\(\PageIndex{1}\).

Los procesos de planarización son vitales para el desarrollo de estructuras multinivel en circuitos VLSI. Para minimizar la resistencia de interconexión y conservar el área del chip, se están desarrollando esquemas de metalización multinivel en los que las interconexiones se ejecutan en 3 dimensiones.

Bibliografía

- J. L. Vossen y W. Kern, Phys. Hoy, 1980, 33, 26.

- S. K. Ghandhi, VLSI Fabrication Principles, Silicio y arseniuro de galio, Wiley, Chichester, 2a Ed. (1994).

- S. M. Sze, Física de los Dispositivos Semiconductores, 2ª Edición, John Wiley & Sons, Nueva York (1981).

- W. E. Beadle, J. C. C. Tsai, R. D. Plummer, Manual de Referencia Rápida para Tecnología de Cuircuit Integrada de Silicio, Wiley, Chichester (1985).

- A. C. Adams y C. D. Capio, J. Electrochem. Soc. , 1981, 128, 2630.