13.4: ADC Flash

- Page ID

- 154605

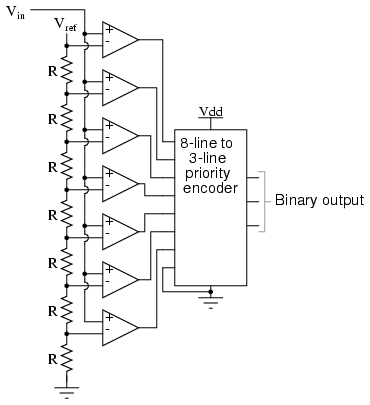

También llamado convertidor A/D paralelo, este circuito es el más simple de entender. Está formado por una serie de comparadores, cada uno comparando la señal de entrada con un voltaje de referencia único. Las salidas del comparador se conectan a las entradas de un circuito codificador de prioridad, que luego produce una salida binaria. La siguiente ilustración muestra un circuito ADC flash de 3 bits:

V ref es un voltaje de referencia estable proporcionado por un regulador de voltaje de precisión como parte del circuito convertidor, no mostrado en el esquema. Como el voltaje de entrada analógica excede el voltaje de referencia en cada comparador, las salidas del comparador se saturarán secuencialmente a un estado alto. El codificador de prioridad genera un número binario basado en la entrada activa de orden más alto, ignorando todas las demás entradas activas.

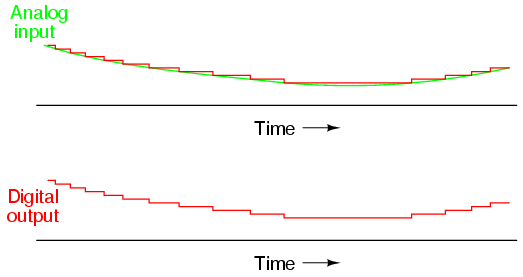

Cuando se opera, el ADC flash produce una salida que se parece a esto:

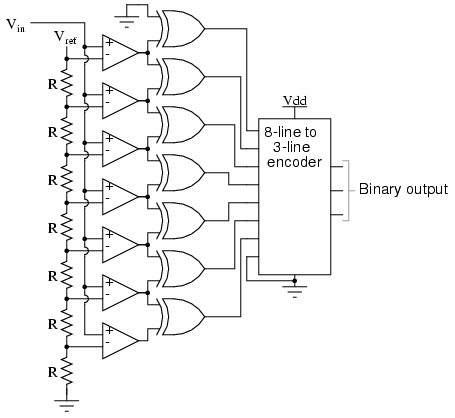

Para esta aplicación en particular, no es necesario un codificador de prioridad regular con toda su complejidad inherente. Debido a la naturaleza de los estados secuenciales de salida del comparador (cada comparador saturando “alto” en secuencia de menor a mayor), el mismo efecto de “selección de entrada de orden más alto” puede realizarse a través de un conjunto de puertas OR exclusivas, permitiendo el uso de un codificador más simple y sin prioridad:

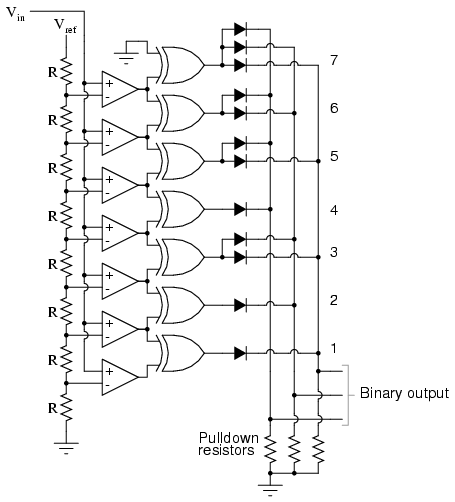

Y, por supuesto, el propio circuito codificador puede estar hecho de una matriz de diodos, lo que demuestra cuán simple se puede construir este diseño de convertidor:

No sólo es el convertidor flash el más simple en términos de teoría operativa, sino que es la más eficiente de las tecnologías ADC en términos de velocidad, estando limitado sólo en retardos de propagación de comparador y puerta. Desafortunadamente, es el componente más intensivo para cualquier número dado de bits de salida. Este ADC flash de tres bits requiere siete comparadores. Una versión de cuatro bits requeriría 15 comparadores. Con cada bit de salida adicional, el número de comparadores requeridos se duplica. Considerando que ocho bits generalmente se considera el mínimo necesario para cualquier ADC práctico (¡se necesitan 255 comparadores!) , la metodología flash muestra rápidamente su debilidad.

Una ventaja adicional del convertidor flash, que a menudo se pasa por alto, es la capacidad de producir una salida no lineal. Con resistencias de igual valor en la red divisora de voltaje de referencia, cada recuento binario sucesivo representa la misma cantidad de aumento de señal analógica, proporcionando una respuesta proporcional. Para aplicaciones especiales, sin embargo, los valores de resistencia en la red divisora pueden hacerse no iguales. Esto le da al ADC una respuesta personalizada y no lineal a la señal de entrada analógica. Ningún otro diseño de ADC es capaz de otorgar este comportamiento de acondicionamiento de señal con solo unos pocos cambios en el valor de los componentes.