13.5: ADC de rampa digital

- Page ID

- 154583

También conocido como la rampa de escalera, o simplemente convertidor A/D contador, esto también es bastante fácil de entender pero desafortunadamente sufre de varias limitaciones.

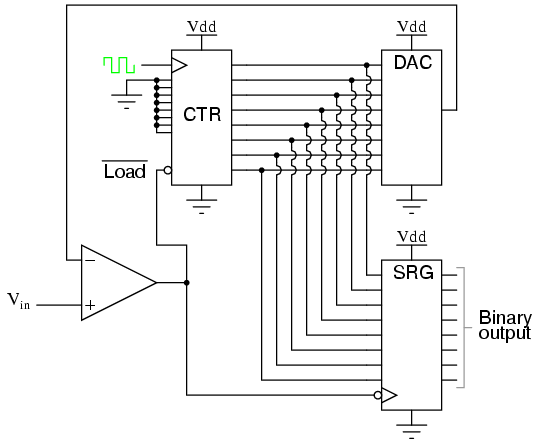

La idea básica es conectar la salida de un contador binario de funcionamiento libre a la entrada de un DAC, luego comparar la salida analógica del DAC con la señal de entrada analógica a digitalizar y usar la salida del comparador para decirle al contador cuándo dejar de contar y reiniciar. El siguiente esquema muestra la idea básica:

A medida que el contador cuenta con cada pulso de reloj, el DAC emite un voltaje ligeramente más alto (más positivo). Este voltaje es comparado con el voltaje de entrada por el comparador. Si el voltaje de entrada es mayor que la salida DAC, la salida del comparador será alta y el contador continuará contando normalmente. Sin embargo, eventualmente, la salida DAC excederá el voltaje de entrada, haciendo que la salida del comparador baje. Esto hará que ocurran dos cosas: primero, la transición de alto a bajo de la salida del comparador hará que el registro de desplazamiento “cargue” cualquier conteo binario que esté siendo enviado por el contador, actualizando así la salida del circuito ADC; en segundo lugar, el contador recibirá una señal baja en la entrada de carga activa-baja, haciendo que se restablezca a 00000000 en el siguiente pulso de reloj.

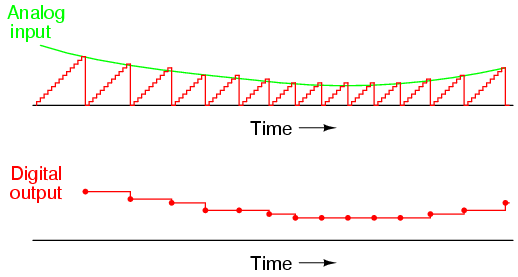

El efecto de este circuito es producir una salida DAC que aumente hasta cualquier nivel en el que se encuentre la señal de entrada analógica, emita el número binario correspondiente a ese nivel y comience de nuevo. Trazar a lo largo del tiempo, se ve así:

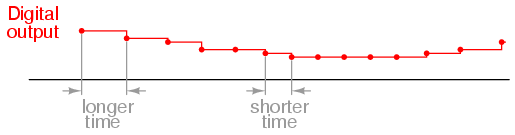

Observe cómo cambia el tiempo entre actualizaciones (nuevos valores de salida digital) dependiendo de qué tan alto sea el voltaje de entrada. Para niveles de señal bajos, las actualizaciones están bastante espaciadas. Para niveles de señal más altos, están más separados en el tiempo:

Para muchas aplicaciones ADC, esta variación en la frecuencia de actualización (tiempo de muestreo) no sería aceptable. Esto, y el hecho de que la necesidad del circuito de contar todo el camino desde 0 al inicio de cada ciclo de conteo hace que el muestreo de la señal analógica sea relativamente lento, coloca al ADC de rampa digital en desventaja con respecto a otras estrategias de contador.