3.12: Descarga electrostática y cierre

- Page ID

- 86319

\( \newcommand{\vecs}[1]{\overset { \scriptstyle \rightharpoonup} {\mathbf{#1}} } \)

\( \newcommand{\vecd}[1]{\overset{-\!-\!\rightharpoonup}{\vphantom{a}\smash {#1}}} \)

\( \newcommand{\dsum}{\displaystyle\sum\limits} \)

\( \newcommand{\dint}{\displaystyle\int\limits} \)

\( \newcommand{\dlim}{\displaystyle\lim\limits} \)

\( \newcommand{\id}{\mathrm{id}}\) \( \newcommand{\Span}{\mathrm{span}}\)

( \newcommand{\kernel}{\mathrm{null}\,}\) \( \newcommand{\range}{\mathrm{range}\,}\)

\( \newcommand{\RealPart}{\mathrm{Re}}\) \( \newcommand{\ImaginaryPart}{\mathrm{Im}}\)

\( \newcommand{\Argument}{\mathrm{Arg}}\) \( \newcommand{\norm}[1]{\| #1 \|}\)

\( \newcommand{\inner}[2]{\langle #1, #2 \rangle}\)

\( \newcommand{\Span}{\mathrm{span}}\)

\( \newcommand{\id}{\mathrm{id}}\)

\( \newcommand{\Span}{\mathrm{span}}\)

\( \newcommand{\kernel}{\mathrm{null}\,}\)

\( \newcommand{\range}{\mathrm{range}\,}\)

\( \newcommand{\RealPart}{\mathrm{Re}}\)

\( \newcommand{\ImaginaryPart}{\mathrm{Im}}\)

\( \newcommand{\Argument}{\mathrm{Arg}}\)

\( \newcommand{\norm}[1]{\| #1 \|}\)

\( \newcommand{\inner}[2]{\langle #1, #2 \rangle}\)

\( \newcommand{\Span}{\mathrm{span}}\) \( \newcommand{\AA}{\unicode[.8,0]{x212B}}\)

\( \newcommand{\vectorA}[1]{\vec{#1}} % arrow\)

\( \newcommand{\vectorAt}[1]{\vec{\text{#1}}} % arrow\)

\( \newcommand{\vectorB}[1]{\overset { \scriptstyle \rightharpoonup} {\mathbf{#1}} } \)

\( \newcommand{\vectorC}[1]{\textbf{#1}} \)

\( \newcommand{\vectorD}[1]{\overrightarrow{#1}} \)

\( \newcommand{\vectorDt}[1]{\overrightarrow{\text{#1}}} \)

\( \newcommand{\vectE}[1]{\overset{-\!-\!\rightharpoonup}{\vphantom{a}\smash{\mathbf {#1}}}} \)

\( \newcommand{\vecs}[1]{\overset { \scriptstyle \rightharpoonup} {\mathbf{#1}} } \)

\(\newcommand{\longvect}{\overrightarrow}\)

\( \newcommand{\vecd}[1]{\overset{-\!-\!\rightharpoonup}{\vphantom{a}\smash {#1}}} \)

\(\newcommand{\avec}{\mathbf a}\) \(\newcommand{\bvec}{\mathbf b}\) \(\newcommand{\cvec}{\mathbf c}\) \(\newcommand{\dvec}{\mathbf d}\) \(\newcommand{\dtil}{\widetilde{\mathbf d}}\) \(\newcommand{\evec}{\mathbf e}\) \(\newcommand{\fvec}{\mathbf f}\) \(\newcommand{\nvec}{\mathbf n}\) \(\newcommand{\pvec}{\mathbf p}\) \(\newcommand{\qvec}{\mathbf q}\) \(\newcommand{\svec}{\mathbf s}\) \(\newcommand{\tvec}{\mathbf t}\) \(\newcommand{\uvec}{\mathbf u}\) \(\newcommand{\vvec}{\mathbf v}\) \(\newcommand{\wvec}{\mathbf w}\) \(\newcommand{\xvec}{\mathbf x}\) \(\newcommand{\yvec}{\mathbf y}\) \(\newcommand{\zvec}{\mathbf z}\) \(\newcommand{\rvec}{\mathbf r}\) \(\newcommand{\mvec}{\mathbf m}\) \(\newcommand{\zerovec}{\mathbf 0}\) \(\newcommand{\onevec}{\mathbf 1}\) \(\newcommand{\real}{\mathbb R}\) \(\newcommand{\twovec}[2]{\left[\begin{array}{r}#1 \\ #2 \end{array}\right]}\) \(\newcommand{\ctwovec}[2]{\left[\begin{array}{c}#1 \\ #2 \end{array}\right]}\) \(\newcommand{\threevec}[3]{\left[\begin{array}{r}#1 \\ #2 \\ #3 \end{array}\right]}\) \(\newcommand{\cthreevec}[3]{\left[\begin{array}{c}#1 \\ #2 \\ #3 \end{array}\right]}\) \(\newcommand{\fourvec}[4]{\left[\begin{array}{r}#1 \\ #2 \\ #3 \\ #4 \end{array}\right]}\) \(\newcommand{\cfourvec}[4]{\left[\begin{array}{c}#1 \\ #2 \\ #3 \\ #4 \end{array}\right]}\) \(\newcommand{\fivevec}[5]{\left[\begin{array}{r}#1 \\ #2 \\ #3 \\ #4 \\ #5 \\ \end{array}\right]}\) \(\newcommand{\cfivevec}[5]{\left[\begin{array}{c}#1 \\ #2 \\ #3 \\ #4 \\ #5 \\ \end{array}\right]}\) \(\newcommand{\mattwo}[4]{\left[\begin{array}{rr}#1 \amp #2 \\ #3 \amp #4 \\ \end{array}\right]}\) \(\newcommand{\laspan}[1]{\text{Span}\{#1\}}\) \(\newcommand{\bcal}{\cal B}\) \(\newcommand{\ccal}{\cal C}\) \(\newcommand{\scal}{\cal S}\) \(\newcommand{\wcal}{\cal W}\) \(\newcommand{\ecal}{\cal E}\) \(\newcommand{\coords}[2]{\left\{#1\right\}_{#2}}\) \(\newcommand{\gray}[1]{\color{gray}{#1}}\) \(\newcommand{\lgray}[1]{\color{lightgray}{#1}}\) \(\newcommand{\rank}{\operatorname{rank}}\) \(\newcommand{\row}{\text{Row}}\) \(\newcommand{\col}{\text{Col}}\) \(\renewcommand{\row}{\text{Row}}\) \(\newcommand{\nul}{\text{Nul}}\) \(\newcommand{\var}{\text{Var}}\) \(\newcommand{\corr}{\text{corr}}\) \(\newcommand{\len}[1]{\left|#1\right|}\) \(\newcommand{\bbar}{\overline{\bvec}}\) \(\newcommand{\bhat}{\widehat{\bvec}}\) \(\newcommand{\bperp}{\bvec^\perp}\) \(\newcommand{\xhat}{\widehat{\xvec}}\) \(\newcommand{\vhat}{\widehat{\vvec}}\) \(\newcommand{\uhat}{\widehat{\uvec}}\) \(\newcommand{\what}{\widehat{\wvec}}\) \(\newcommand{\Sighat}{\widehat{\Sigma}}\) \(\newcommand{\lt}{<}\) \(\newcommand{\gt}{>}\) \(\newcommand{\amp}{&}\) \(\definecolor{fillinmathshade}{gray}{0.9}\)

Como probablemente sepa, hay que tener mucho cuidado al manejar los circuitos MOS para asegurarse de que está debidamente conectado a tierra, y que no transfiera ninguna electricidad estática al chip. El modelo estándar de cuerpo humano asume una transferencia de carga estática de aproximadamente 0.1 micro-culombios\(10^{-7} \mathrm{C}\) tras la descarga de electricidad estática entre un humano y un chip. Esto no parece suficiente carga para hacer ningún daño hasta que no recordemos la vieja fórmula:\[Q = CV\] o\[V = \frac{Q}{C}\]

La última vez que miré,\(10^{-7}\) dividido por\(10^{-14}\) es de unos\(10^{7}\) voltios! Agregue a esto el hecho de que el espesor del óxido de la puerta es solo sobre\(10^{-6} \mathrm{~cm}\), así que tenemos campos eléctricos en el óxido de la puerta que están en el orden de\(10^{13} \ \frac{\mathrm{V}}{\mathrm{cm}}\)! No me extraña que las cosas se rompan. Este problema se llama descarga electrostática, o ESD, y es una de las principales preocupaciones de los fabricantes de CI. Proteger contra la EDS sigue siendo en gran medida un “arte negro” y es algo que la gente sigue estudiando bastante. Los JFET son estructuras mucho más resistentes con capacitancias de compuerta mucho más altas y no son tan propensos a fallas ESD.

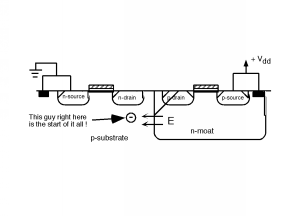

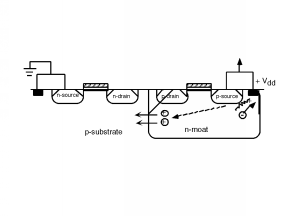

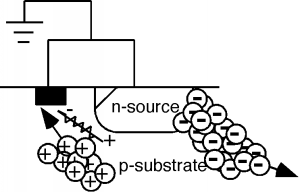

Ya que estamos en el tema de los problemas, echemos un vistazo a una “falla” más que afecta a los diseñadores de CI. Tenemos que volver al circuito CMOS. Recuerde, la unión moco/sustrato es de polarización inversa, por lo que tendremos un campo eléctrico en la región de agotamiento de esa unión, apuntando como se muestra en la Figura\(\PageIndex{1}\).

Figura\(\PageIndex{1}\): ¡El inicio de los problemas!

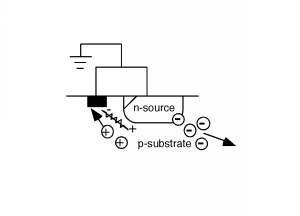

Figura\(\PageIndex{1}\): ¡El inicio de los problemas!Supongamos, de alguna manera, que tenemos uno o más electrones desviados en el sustrato tipo p. Serán barridos a través del cruce sustrato/foso por el campo eléctrico, y serán atraídos por el contacto del foso por\(V_{\text{dd}}\). Centrémonos en lo que sucede a medida que el electrón fluye fuera del\(V_{\text{dd}}\) contacto (Figura\(\PageIndex{2}\)).

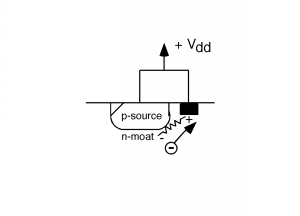

A medida que el electrón se mueve a través del material de foso de tipo n (resistivo), desarrolla una caída de voltaje entre el material de tipo n bajo la fuente, y el\(V_{\text{dd}}\) contacto (que también está en el potencial de la fuente ya que están conectados entre sí por la interconexión en la superficie de la oblea). El flujo de electrones en una dirección significa el flujo de corriente en la otra, y así esto hace que la región debajo de la fuente sea ligeramente negativa con respecto a la región fuente misma. Esto, por supuesto, sesga ligeramente hacia adelante la unión fuente/foso, lo que provoca que se inyecte un agujero o dos en el foso desde la fuente p (Figura\(\PageIndex{3}\)).

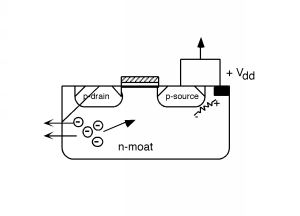

Figura\(\PageIndex{3}\): La fuente sesgada hacia delante inyecta algunos agujeros

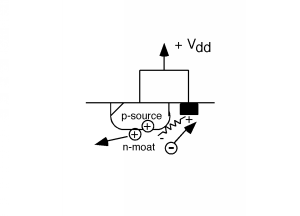

Figura\(\PageIndex{3}\): La fuente sesgada hacia delante inyecta algunos agujerosLos agujeros serán atraídos por el campo a través de la capa de agotamiento de sustrato de foso y, una vez que lleguen allí, serán barridos hacia el sustrato p (Figura\(\PageIndex{4}\)).

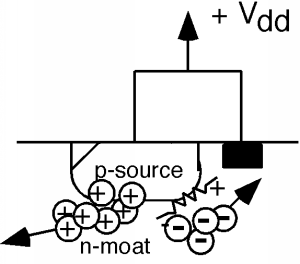

Una vez que los agujeros entren en el sustrato p, serán atraídos por la conexión a tierra para que puedan abandonar el semiconductor. A medida que estos agujeros fluyen más allá de la fuente n, y a través del sustrato p resistivo, construyen un potencial entre el contacto de tierra (Figura\(\PageIndex{5}\)), y el material debajo de la fuente con una polaridad que tiende a polarizar hacia adelante la unión fuente-sustrato, y hacer que los electrones sean inyectados en el sustrato. Los electrones, a su vez, son atraídos al campo a través de la unión sustrato-foso (Figura\(\PageIndex{6}\)).

Algunos de los electrones pueden recombinarse en la región p, pero en los sustratos de alta calidad actuales, hay muy pocos centros de recombinación activos, por lo que a pesar de que los electrones son portadores minoritarios, tienen una vida útil bastante larga de los portadores minoritarios, y la mayoría de ellos llegan a la unión sustrato-foso y son barrió en el foso. Una vez dentro del foso n, los electrones son atraídos por el\(+V_{\text{dd}}\) contacto, donde, por supuesto, construyen un mayor sesgo hacia adelante a través de la unión fuente-foso, provocando que se emitan más agujeros desde la fuente hacia el foso (Figura\(\PageIndex{7}\)). Estos agujeros se barren a través de la unión moso-sustrato, fluyen hacia el contacto con el suelo y, bueno... ¡ya entiende la idea! No pasa mucho tiempo antes de que tengamos un cortocircuito muerto entre Vdd y tierra. Esto no es saludable para los chips de circuito integrado en lo más mínimo, y es un proceso llamado latch-up (Figura\(\PageIndex{8}\)).

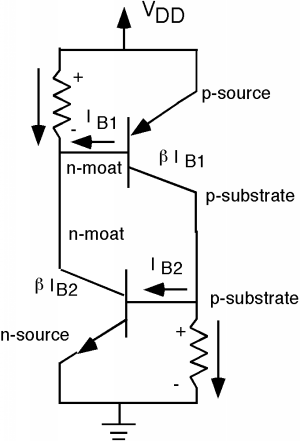

Hay un circuito interesante que puedes dibujar que muestra lo que está sucediendo desde un punto de vista algo diferente. Tenga en cuenta que podemos considerar la fuente p, el foso n y el sustrato p como un transistor bipolar pnp. También la fuente n, el sustrato p y el foso n también forman un transistor bipolar npn fino. Sin embargo, los dos transistores se entremezclan, con la base del pnp y los colectores del npn compartiendo el mismo n-foso, y el colector del pnp y la base del npn compartiendo el p-sustrato. Los sustratos n-foso y p son colectores y bases al mismo tiempo. Una pequeña inspección cuidadosa de la sección transversal del inversor CMOS le llevará al siguiente esquema que se muestra en la Figura\(\PageIndex{9}\). Necesitamos algo para poner en marcha este circuito, así que digamos que tenemos un poco de corriente de colector saliendo del transistor pnp superior. Esta corriente fluye hacia abajo, a través de la resistencia a tierra. A medida que fluye a través de la resistencia, acumula un poco de voltaje que polariza hacia adelante la unión base-emisor del transistor inferior, npn, y hace que algo de corriente del colector fluya hacia él. Esta corriente viene\(V_{\text{dd}}\) a través de la resistencia superior, y acumula un voltaje a través de esa resistencia que polarizará hacia adelante la unión base-emisor del transistor superior, pnp. Esto, a su vez, hace que alguna corriente adicional del colector fluya fuera del transistor pnp, ¡y lejos nos vamos! Latch-up es malo, y es algo que los diseñadores de CI trabajan muy duro para evitar.

Quizás te preguntes qué es lo que realmente inicia un circuito entrando en traba. Consulte de nuevo al inversor CMOS y tenga en cuenta que el n-drain en el NMOS está conectado a la salida. La salida podría ser una salida real, yendo más allá del chip hacia el “mundo real”. Si el “cliente” que está usando el chip es descuidado, y de alguna manera arrastra la salida por debajo del suelo, la unión drenaje/p-sustrato será polarizada hacia adelante, los electrones serán inyectados en el sustrato p, y estamos de vuelta en la Figura\(\PageIndex{1}\). Los diseñadores de CI intentan mantener el\(V_{\text{dd}}\) contacto n-moat/ lo más cerca posible de la fuente PMOS, y el contacto p-sustrato/tierra lo más cerca posible de la fuente NMOS para reducir la resistencia entre las regiones de contacto y fuente, y por lo tanto disminuir la posibilidad de que el circuito entre en enganche.