13.6: Aproximación sucesiva ADC

- Page ID

- 154563

Un método para abordar las deficiencias del ADC de rampa digital es el llamado ADC de aproximación sucesiva. El único cambio en este diseño es un circuito contador muy especial conocido como registro de aproximación sucesiva. En lugar de contar en secuencia binaria, este registro cuenta probando todos los valores de bits comenzando con el bit más significativo y terminando en el bit menos significativo. A lo largo del proceso de conteo, el registro monitorea la salida del comparador para ver si el conteo binario es menor o mayor que la entrada de señal analógica, ajustando los valores de bit en consecuencia. La forma en que el registro cuenta es idéntica al método de “prueba y ajuste” de conversión decimal a binario, mediante el cual se prueban diferentes valores de bits de MSB a LSB para obtener un número binario que sea igual al número decimal original. La ventaja de esta estrategia de conteo son resultados mucho más rápidos: la salida DAC converge en la entrada de señal analógica en pasos mucho más grandes que con la secuencia de conteo de 0 a completo de un contador regular.

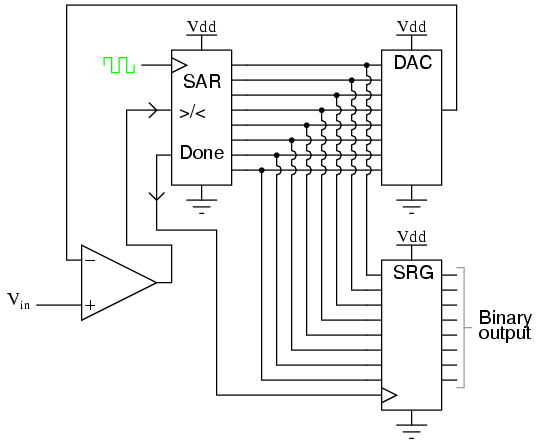

Sin mostrar el funcionamiento interno del registro de aproximaciones sucesivas (SAR), el circuito se ve así:

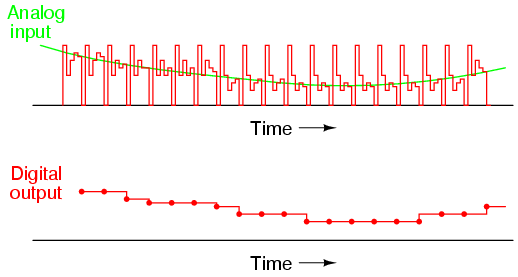

Cabe señalar que el SAR es generalmente capaz de emitir el número binario en formato serie (un bit a la vez), eliminando así la necesidad de un registro de turno. Trazado a lo largo del tiempo, la operación de un ADC de aproximación sucesiva se ve así:

Observe cómo las actualizaciones para este ADC ocurren a intervalos regulares, a diferencia del circuito ADC de rampa digital.