13.8: ADC de pendiente (integrador)

- Page ID

- 154564

Hasta ahora, solo hemos podido escapar del gran volumen de componentes en el convertidor de flash mediante el uso de un DAC como parte de nuestro circuito ADC. Sin embargo, esta no es nuestra única opción. Es posible evitar el uso de un DAC si sustituimos un circuito de rampa analógico y un contador digital con sincronización precisa.

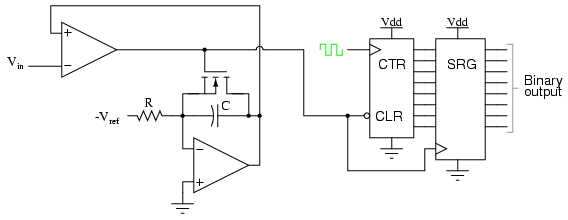

El es la idea básica detrás de la llamada pendiente única, o ADC integrador. En lugar de usar un DAC con una salida en rampa, usamos un circuito de amplificador operacional llamado integrador para generar una forma de onda de diente de sierra que luego se compara con la entrada analógica por un comparador. El tiempo que tarda la forma de onda en diente de sierra en superar el nivel de voltaje de la señal de entrada se mide por medio de un contador digital sincronizado con una onda cuadrada de frecuencia precisa (generalmente de un oscilador de cristal). El diagrama esquemático básico se muestra aquí:

El esquema de transistor de descarga de condensador IGFET que se muestra aquí es un poco simplificado. En realidad, un circuito de enganche sincronizado con la señal de reloj probablemente tendría que estar conectado a la puerta IGFET para asegurar la descarga completa del condensador cuando la salida del comparador va alta. La idea básica, sin embargo, es evidente en este diagrama. Cuando la salida del comparador es baja (voltaje de entrada mayor que la salida del integrador), el integrador puede cargar el condensador de manera lineal. En tanto, el contador está contando a una velocidad fijada por la frecuencia del reloj de precisión. El tiempo que tarda el condensador en cargarse hasta el mismo nivel de voltaje que la entrada depende del nivel de señal de entrada y la combinación de -V ref, R y C. Cuando el condensador alcanza ese nivel de voltaje, la salida del comparador va alta, cargando la salida del contador en el registro de desplazamiento para un salida final. El IGFET se activa “on” por la salida alta del comparador, descargando el condensador de nuevo a cero voltios. Cuando el voltaje de salida del integrador cae a cero, la salida del comparador vuelve a un estado bajo, limpiando el contador y permitiendo que el integrador aumente el voltaje nuevamente.

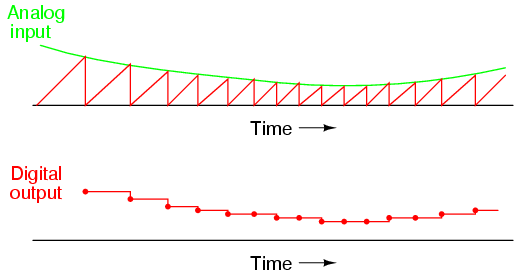

Este circuito ADC se comporta de manera muy similar al ADC de rampa digital, excepto que el voltaje de referencia del comparador es una forma de onda de diente de sierra suave en lugar de una “escalera”:

El ADC de pendiente única sufre todas las desventajas del ADC de rampa digital, con el inconveniente agregado de la deriva de calibración. La correspondencia precisa de la salida de este ADC con su entrada depende de que la pendiente de voltaje del integrador se ajuste a la tasa de conteo del contador (la frecuencia de reloj). Con el ADC de rampa digital, la frecuencia del reloj no tuvo efecto en la precisión de la conversión, solo en el tiempo de actualización. En este circuito, dado que la tasa de integración y la tasa de conteo son independientes entre sí, la variación entre los dos es inevitable a medida que envejece, y resultará en una pérdida de precisión. Lo único bueno que decir de este circuito es que evita el uso de un DAC, lo que reduce la complejidad del circuito.

Una respuesta a este dilema de deriva de calibración se encuentra en una variación de diseño llamada convertidor de doble pendiente. En el convertidor de doble pendiente, un circuito integrador se acciona positivo y negativo en ciclos alternos para bajar y luego subir, en lugar de ser reajustado a 0 voltios al final de cada ciclo. En una dirección de rampa, el integrador es impulsado por la señal de entrada analógica positiva (produciendo una tasa variable negativa de cambio de voltaje de salida, o pendiente de salida) durante una cantidad de tiempo fija, medida por un contador con un reloj de frecuencia de precisión. Entonces, en la otra dirección, con un voltaje de referencia fijo (produciendo una tasa fija de cambio de voltaje de salida) con tiempo medido por el mismo contador. El contador deja de contar cuando la salida del integrador alcanza el mismo voltaje que cuando inició la porción de tiempo fijo del ciclo. La cantidad de tiempo que tarda el condensador del integrador en descargarse de nuevo a su voltaje de salida original, medido por la magnitud acumulada por el contador, se convierte en la salida digital del circuito ADC.

El método de doble pendiente se puede pensar de manera análoga en términos de un resorte giratorio como el utilizado en un mecanismo de reloj mecánico. Imagina que estábamos construyendo un mecanismo para medir la velocidad de rotación de un eje. Por lo tanto, la velocidad del eje es nuestra “señal de entrada” para ser medida por este dispositivo. El ciclo de medición comienza con la primavera en un estado relajado. Luego, el resorte es girado o “enrollado” por el eje giratorio (señal de entrada) durante un período de tiempo fijo. Esto coloca al resorte en una cierta cantidad de tensión proporcional a la velocidad del eje: una mayor velocidad del eje corresponde a una velocidad de enrollamiento más rápida. y una mayor cantidad de tensión del resorte acumulada durante ese período de tiempo. Después de eso, el resorte se desacopla del eje y se le permite desenrollarse a una velocidad fija, el tiempo para que se desenrolle de nuevo a un estado relajado medido por un dispositivo temporizador. La cantidad de tiempo que tarda el resorte en desenrollarse a esa velocidad fija será directamente proporcional a la velocidad a la que se enrolló (magnitud de la señal de entrada) durante la porción de tiempo fijo del ciclo.

Esta técnica de conversión analógico-digital escapa al problema de deriva de calibración del ADC de pendiente única porque tanto el coeficiente de integración del integrador (o “ganancia”) como la tasa de velocidad del contador están vigentes durante todas las partes del ciclo de “bobinado” y “desenrollado”. Si la velocidad del reloj del contador aumentara repentinamente, esto acortaría el período de tiempo fijo donde el integrador “termina” (resultando en una menor tensión acumulada por el integrador), pero también significaría que contaría más rápido durante el periodo de tiempo en que se le permitió al integrador “desenrollarse” en una tasa fija. La proporción en la que el contador esté contando más rápido será la misma proporción que el voltaje acumulado del integrador disminuye desde antes del cambio de velocidad del reloj. Así, el error de velocidad del reloj se cancelaría por sí mismo y la salida digital sería exactamente lo que debería ser.

Otra ventaja importante de este método es que la señal de entrada se promedia a medida que acciona el integrador durante la porción de tiempo fijo del ciclo. Cualquier cambio en la señal analógica durante ese período de tiempo tiene un efecto acumulativo en la salida digital al final de ese ciclo. Otras estrategias ADC simplemente “capturan” el nivel de señal analógica en un solo punto en el tiempo cada ciclo. Si la señal analógica es “ruidosa” (contiene niveles significativos de picos de tensión/inmersiones espurias), una de las otras tecnologías de convertidor ADC puede convertir ocasionalmente un pico o dip porque captura la señal repetidamente en un solo punto en el tiempo. Un ADC de doble pendiente, por otro lado, promedia en conjunto todos los picos y caídas dentro del periodo de integración, proporcionando así una salida con mayor inmunidad al ruido. Los ADC de doble pendiente se utilizan en aplicaciones que exigen alta precisión.