13.9: ADC Delta-Sigma

- Page ID

- 154570

Una de las tecnologías ADC más avanzadas es la llamada delta-sigma, o Δ( usando la notación de letras griegas propiamente dicha). En matemáticas y física, la letra griega mayúscula delta (Δ) representa diferencia o cambio, mientras que la letra mayúscula sigma (σ) representa la suma: la adición de múltiples términos juntos. A veces este convertidor es referido por las mismas letras griegas en orden inverso: sigma-delta, o σΔ.

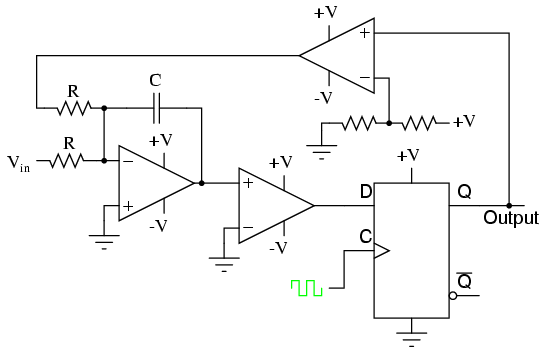

En un convertidor Δ, la señal de voltaje de entrada analógica se conecta a la entrada de un integrador, produciendo una tasa de cambio de voltaje, o pendiente, en la salida correspondiente a la magnitud de entrada. Este voltaje de rampa es luego comparado con el potencial de tierra (0 voltios) por un comparador. El comparador actúa como una especie de ADC de 1 bit, produciendo 1 bit de salida (“alto” o “bajo”) dependiendo de si la salida del integrador es positiva o negativa. La salida del comparador se bloquea a través de un flip-flop tipo D sincronizado a alta frecuencia, y se realimenta a otro canal de entrada en el integrador, para accionar el integrador en la dirección de una salida de 0 voltios. El circuito básico se ve así:

El amplificador operacional más a la izquierda es el integrador (sumador). El siguiente amplificador operacional al que alimenta el integrador es el comparador, o ADC de 1 bit. Luego viene el flip-flop tipo D, que bloquea la salida del comparador en cada pulso de reloj, enviando ya sea una señal “alta” o “baja” al siguiente comparador en la parte superior del circuito. Este comparador final es necesario para convertir el voltaje de salida de nivel lógico de 0V/5V de polaridad única del flip-flop en una señal de voltaje de +V/-V para ser realimentada al integrador.

Si la salida del integrador es positiva, el primer comparador emitirá una señal “alta” a la entrada D del flip-flop. En el siguiente pulso de reloj, esta señal “alta” se emitirá desde la línea Q a la entrada no inversora del último comparador. Este último comparador, al ver una tensión de entrada mayor que la tensión umbral de 1/2 +V, se satura en una dirección positiva, enviando una señal +V completa a la otra entrada del integrador. Esta señal de realimentación +V tiende a impulsar la salida del integrador en una dirección negativa. Si ese voltaje de salida alguna vez se vuelve negativo, el bucle de retroalimentación enviará una señal correctiva (-V) de vuelta a la entrada superior del integrador para conducirlo en una dirección positiva. Este es el concepto delta-sigma en acción: el primer comparador detecta una diferencia (Δ) entre la salida del integrador y cero voltios. El integrador suma (σ) la salida del comparador con la señal de entrada analógica.

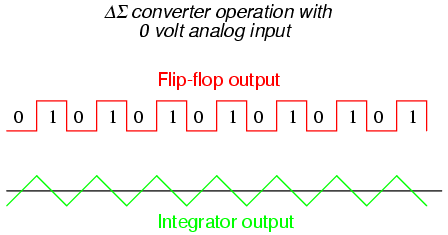

Funcionalmente, esto da como resultado un flujo en serie de bits emitidos por el flip-flop. Si la entrada analógica es de cero voltios, el integrador no tendrá tendencia a rampa ni positiva ni negativa, excepto en respuesta a la tensión de realimentación. En este escenario, la salida del flip-flop oscilará continuamente entre “alta” y “baja”, a medida que el sistema de retroalimentación “caza” de un lado a otro, tratando de mantener la salida del integrador a cero voltios:

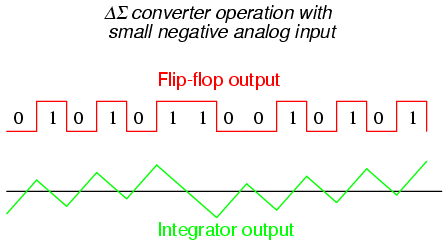

Sin embargo, si aplicamos una tensión de entrada analógica negativa, el integrador tendrá una tendencia a aumentar su salida en una dirección positiva. La retroalimentación solo puede agregar a la rampa del integrador por un voltaje fijo durante un tiempo fijo, y así la salida de flujo de bits por el flip-flop no será del todo lo mismo:

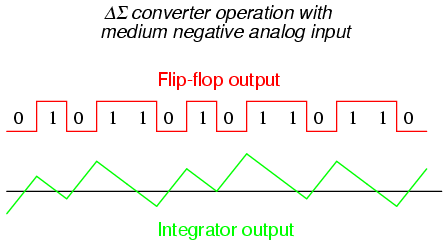

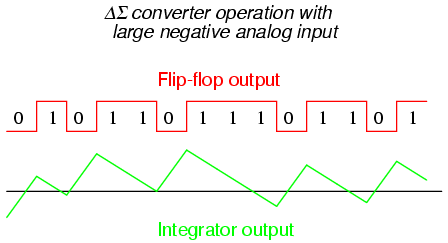

Al aplicar una señal de entrada analógica más grande (negativa) al integrador, forzamos su salida a rampa más pronunciada en la dirección positiva. Por lo tanto, el sistema de retroalimentación tiene que emitir más 1's que antes para devolver la salida del integrador a cero voltios:

A medida que la señal de entrada analógica aumenta en magnitud, también lo hace la ocurrencia de 1's en la salida digital del flip-flop:

Una salida de número binario paralelo se obtiene de este circuito promediando el flujo en serie de bits juntos. Por ejemplo, un circuito contador podría diseñarse para recoger el número total de salidas de 1 por el flip-flop en un número dado de pulsos de reloj. Este recuento sería entonces indicativo de la tensión de entrada analógica.

Existen variaciones sobre este tema, empleando múltiples etapas integradoras y/o circuitos comparadores que dan salida a más de 1 bit, pero un concepto común a todos los convertidores Δes el de sobremuestreo. El sobremuestreo es cuando un ADC toma múltiples muestras de una señal analógica (en este caso, un ADC de 1 bit), y esas muestras digitalizadas se promedian. El resultado final es un aumento efectivo en el número de bits resueltos a partir de la señal. En otras palabras, un ADC de 1 bit sobremuestreado puede hacer el mismo trabajo que un ADC de 8 bits con muestreo de una sola vez, aunque a una velocidad más lenta.