3.10: Lógica CMOS

- Page ID

- 86390

\( \newcommand{\vecs}[1]{\overset { \scriptstyle \rightharpoonup} {\mathbf{#1}} } \)

\( \newcommand{\vecd}[1]{\overset{-\!-\!\rightharpoonup}{\vphantom{a}\smash {#1}}} \)

\( \newcommand{\dsum}{\displaystyle\sum\limits} \)

\( \newcommand{\dint}{\displaystyle\int\limits} \)

\( \newcommand{\dlim}{\displaystyle\lim\limits} \)

\( \newcommand{\id}{\mathrm{id}}\) \( \newcommand{\Span}{\mathrm{span}}\)

( \newcommand{\kernel}{\mathrm{null}\,}\) \( \newcommand{\range}{\mathrm{range}\,}\)

\( \newcommand{\RealPart}{\mathrm{Re}}\) \( \newcommand{\ImaginaryPart}{\mathrm{Im}}\)

\( \newcommand{\Argument}{\mathrm{Arg}}\) \( \newcommand{\norm}[1]{\| #1 \|}\)

\( \newcommand{\inner}[2]{\langle #1, #2 \rangle}\)

\( \newcommand{\Span}{\mathrm{span}}\)

\( \newcommand{\id}{\mathrm{id}}\)

\( \newcommand{\Span}{\mathrm{span}}\)

\( \newcommand{\kernel}{\mathrm{null}\,}\)

\( \newcommand{\range}{\mathrm{range}\,}\)

\( \newcommand{\RealPart}{\mathrm{Re}}\)

\( \newcommand{\ImaginaryPart}{\mathrm{Im}}\)

\( \newcommand{\Argument}{\mathrm{Arg}}\)

\( \newcommand{\norm}[1]{\| #1 \|}\)

\( \newcommand{\inner}[2]{\langle #1, #2 \rangle}\)

\( \newcommand{\Span}{\mathrm{span}}\) \( \newcommand{\AA}{\unicode[.8,0]{x212B}}\)

\( \newcommand{\vectorA}[1]{\vec{#1}} % arrow\)

\( \newcommand{\vectorAt}[1]{\vec{\text{#1}}} % arrow\)

\( \newcommand{\vectorB}[1]{\overset { \scriptstyle \rightharpoonup} {\mathbf{#1}} } \)

\( \newcommand{\vectorC}[1]{\textbf{#1}} \)

\( \newcommand{\vectorD}[1]{\overrightarrow{#1}} \)

\( \newcommand{\vectorDt}[1]{\overrightarrow{\text{#1}}} \)

\( \newcommand{\vectE}[1]{\overset{-\!-\!\rightharpoonup}{\vphantom{a}\smash{\mathbf {#1}}}} \)

\( \newcommand{\vecs}[1]{\overset { \scriptstyle \rightharpoonup} {\mathbf{#1}} } \)

\(\newcommand{\longvect}{\overrightarrow}\)

\( \newcommand{\vecd}[1]{\overset{-\!-\!\rightharpoonup}{\vphantom{a}\smash {#1}}} \)

\(\newcommand{\avec}{\mathbf a}\) \(\newcommand{\bvec}{\mathbf b}\) \(\newcommand{\cvec}{\mathbf c}\) \(\newcommand{\dvec}{\mathbf d}\) \(\newcommand{\dtil}{\widetilde{\mathbf d}}\) \(\newcommand{\evec}{\mathbf e}\) \(\newcommand{\fvec}{\mathbf f}\) \(\newcommand{\nvec}{\mathbf n}\) \(\newcommand{\pvec}{\mathbf p}\) \(\newcommand{\qvec}{\mathbf q}\) \(\newcommand{\svec}{\mathbf s}\) \(\newcommand{\tvec}{\mathbf t}\) \(\newcommand{\uvec}{\mathbf u}\) \(\newcommand{\vvec}{\mathbf v}\) \(\newcommand{\wvec}{\mathbf w}\) \(\newcommand{\xvec}{\mathbf x}\) \(\newcommand{\yvec}{\mathbf y}\) \(\newcommand{\zvec}{\mathbf z}\) \(\newcommand{\rvec}{\mathbf r}\) \(\newcommand{\mvec}{\mathbf m}\) \(\newcommand{\zerovec}{\mathbf 0}\) \(\newcommand{\onevec}{\mathbf 1}\) \(\newcommand{\real}{\mathbb R}\) \(\newcommand{\twovec}[2]{\left[\begin{array}{r}#1 \\ #2 \end{array}\right]}\) \(\newcommand{\ctwovec}[2]{\left[\begin{array}{c}#1 \\ #2 \end{array}\right]}\) \(\newcommand{\threevec}[3]{\left[\begin{array}{r}#1 \\ #2 \\ #3 \end{array}\right]}\) \(\newcommand{\cthreevec}[3]{\left[\begin{array}{c}#1 \\ #2 \\ #3 \end{array}\right]}\) \(\newcommand{\fourvec}[4]{\left[\begin{array}{r}#1 \\ #2 \\ #3 \\ #4 \end{array}\right]}\) \(\newcommand{\cfourvec}[4]{\left[\begin{array}{c}#1 \\ #2 \\ #3 \\ #4 \end{array}\right]}\) \(\newcommand{\fivevec}[5]{\left[\begin{array}{r}#1 \\ #2 \\ #3 \\ #4 \\ #5 \\ \end{array}\right]}\) \(\newcommand{\cfivevec}[5]{\left[\begin{array}{c}#1 \\ #2 \\ #3 \\ #4 \\ #5 \\ \end{array}\right]}\) \(\newcommand{\mattwo}[4]{\left[\begin{array}{rr}#1 \amp #2 \\ #3 \amp #4 \\ \end{array}\right]}\) \(\newcommand{\laspan}[1]{\text{Span}\{#1\}}\) \(\newcommand{\bcal}{\cal B}\) \(\newcommand{\ccal}{\cal C}\) \(\newcommand{\scal}{\cal S}\) \(\newcommand{\wcal}{\cal W}\) \(\newcommand{\ecal}{\cal E}\) \(\newcommand{\coords}[2]{\left\{#1\right\}_{#2}}\) \(\newcommand{\gray}[1]{\color{gray}{#1}}\) \(\newcommand{\lgray}[1]{\color{lightgray}{#1}}\) \(\newcommand{\rank}{\operatorname{rank}}\) \(\newcommand{\row}{\text{Row}}\) \(\newcommand{\col}{\text{Col}}\) \(\renewcommand{\row}{\text{Row}}\) \(\newcommand{\nul}{\text{Nul}}\) \(\newcommand{\var}{\text{Var}}\) \(\newcommand{\corr}{\text{corr}}\) \(\newcommand{\len}[1]{\left|#1\right|}\) \(\newcommand{\bbar}{\overline{\bvec}}\) \(\newcommand{\bhat}{\widehat{\bvec}}\) \(\newcommand{\bperp}{\bvec^\perp}\) \(\newcommand{\xhat}{\widehat{\xvec}}\) \(\newcommand{\vhat}{\widehat{\vvec}}\) \(\newcommand{\uhat}{\widehat{\uvec}}\) \(\newcommand{\what}{\widehat{\wvec}}\) \(\newcommand{\Sighat}{\widehat{\Sigma}}\) \(\newcommand{\lt}{<}\) \(\newcommand{\gt}{>}\) \(\newcommand{\amp}{&}\) \(\definecolor{fillinmathshade}{gray}{0.9}\)Considera lo siguiente, que se muestra en la Figura\(\PageIndex{1}\).

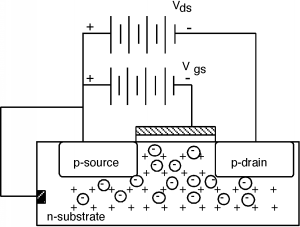

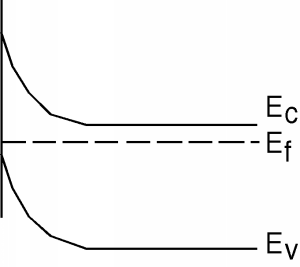

Esto se parece mucho a nuestro MOSFET anterior excepto que ahora tenemos un sustrato tipo n y las regiones de origen y drenaje son de tipo p. Si aplicamos un negativo\(V_{\text{gs}}\) (con la fuente conectada al sustrato tipo n) entonces la carga negativa inducida en la puerta alejará los electrones, y si las bandas debajo de la puerta están suficientemente dobladas hacia arriba, forman una capa de inversión de agujeros (ver Figura\(\PageIndex{2}\), así hacer un MOSFET de canal p en modo de mejora o un transistor PMOS. (A diferencia de un transistor NMOS que estudiamos primero.). Tenga en cuenta que un transistor PMOS tendrá un negativo\(V_{T}\). Es decir, el voltaje de puerta tiene que ser menor que el voltaje de fuente/sustrato para encender el dispositivo. Cuanto más negativo\(V_{\text{gs}}\) es, más corriente tendremos fluyendo a través del dispositivo.

Resulta que una combinación tanto de un dispositivo de canal n como de canal p en el mismo circuito puede ser muy ventajosa. Dicha tecnología se llama CMOS, por “MOS complementarios”. Así es como usamos un transistor de canal p en el circuito inversor.

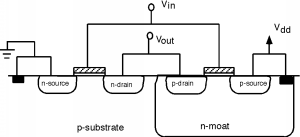

En primer lugar, sin embargo, tenemos que ver cómo haríamos uno. Existe un problema fundamental al tratar de usar dispositivos tanto de canal n como de canal p en el mismo circuito. ¿Qué es? Parecería que necesitamos dos tipos diferentes de sustratos, tanto un sustrato tipo p para el transistor de canal n como un sustrato tipo n para el dispositivo de canal p. Hay una forma de evitar este problema haciendo lo que se llama un tanque o un foso. Un foso es una región relativamente profunda de un tipo de material colocado en un sustrato huésped del tipo opuesto (Figura\(\PageIndex{3}\)). Podemos poner regiones de fuente/drenaje de tipo n en el sustrato p y regiones de fuente/drenaje tipo p en el foso n. En la Figura\(\PageIndex{4}\), también mostraremos las puertas, y cómo todo el inversor está conectado entre sí.

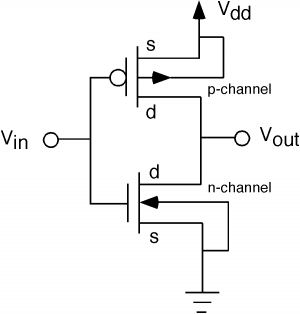

Ahora dibujemos el esquema: Un dispositivo de canal p se dibuja igual que un dispositivo de n canales, excepto que ponemos una pequeña “burbuja” en la puerta para significar que es un MOSFET de un color diferente. Aunque normalmente no hacemos esto todo el tiempo, también hemos mostrado las conexiones de sustrato en este diagrama. Estas conexiones muestran que un MOSFET es al menos un dispositivo de cuatro terminales, no uno de tres terminales como suele suponer la gente. Dado que, en un dispositivo de canal p, el sustrato es de tipo n, mostramos la conexión del sustrato como una flecha que apunta hacia afuera. El sustrato tipo p para el dispositivo de canal n se muestra como una flecha que apunta hacia adentro. El sustrato de canal n está conectado a tierra, y el sustrato de canal p está conectado a\(V_{\text{dd}}\). Tenga en cuenta que dado que el foso n está en\(V_{\text{dd}}\) y el sustrato p está en el suelo, la unión p-n de sustrato de foso es de polarización inversa, por lo que no debe fluir corriente entre ellos.

Por lo general, tampoco etiquetamos la fuente y drenamos, pero lo hacemos aquí, solo por completitud. Tenga en cuenta que a diferencia del transistor bipolar, el FET es realmente un dispositivo simétrico. Realmente no hay forma de decir la fuente desde el desagüe. Por convención, llamamos al elemento que está conectado al sustrato (o foso) la fuente, y al otro el drenaje. A veces escuchará la región debajo de la puerta (ya sea sustrato o foso) conocida como el backbody.

Ahora veamos cómo funciona este circuito. Si\(V_{\text{in}}\) es alto (en o cerca\(V_{\text{dd}}\)) el transistor NMOS se encenderá. El voltaje entre la puerta y el sustrato del dispositivo de canal p está en o cerca de cero. ¡La puerta está en\(V_{\text{dd}}\) y también el foso! De ahí que el transistor superior se apagará. La salida será así baja.

Si el voltaje de entrada está en o cerca de tierra (un “bajo”), entonces el dispositivo de canal n se apaga. El voltaje entre la puerta y el sustrato del dispositivo de canal p es ahora\(\simeq \left( -V_{\text{dd}} \right)\). (La puerta es\(\simeq 0\) y el sustrato está en\(V_{\text{dd}}\).) Si el transistor PMOS tiene un voltaje umbral\(V_{T}\) de, digamos\(-2 \mathrm{~V}\),, entonces se encenderá y la salida será alta. Sin embargo, tenga en cuenta que en cualquier estado, alto o bajo, no hay corriente estática que fluya a través del inversor.

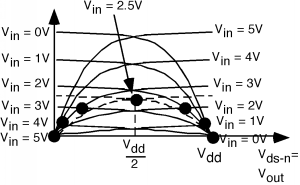

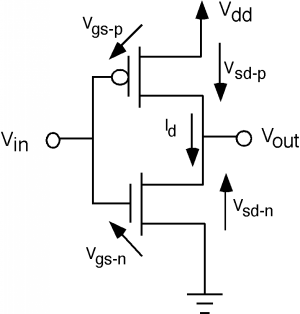

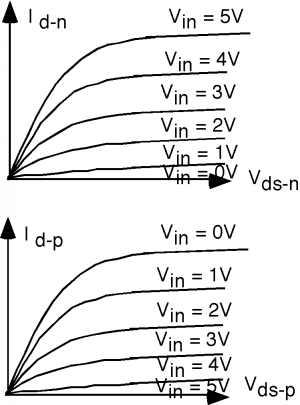

Las características de transferencia para este circuito son un poco más complicadas. Primero, asegurémonos de tener nuestros voltajes y corrientes definidos. De la Figura\(\PageIndex{6}\), el voltaje puerta-fuente de canal n,\(V_{\text{gs-}n}\), es justo\(V_{\text{in}}\). El voltaje puerta-fuente para el dispositivo de canal p,\(V_{\text{gs-}p}\), es\(V_{\text{in}} - V_{\text{dd}\);\(V_{\text{ds-}p}\), el voltaje dreno-fuente para el transistor de canal p se puede escribir como\(V_{\text{ds-}n} - V_{\text{dd}}\). Para corriente,\(I_{d \text{-} n} = I_{d \text{-} p} = I_{d}\). Como se ve en la Figura\(\PageIndex{7}\), tenemos dos conjuntos de curvas características. Tenga en cuenta que desde\(V_{\text{gs-}p} = V_{\text{in}} - V_{\text{dd}}\)\(V_{\text{in}} = 0 \mathrm{~V}\), cuando,\(V_{\text{gs-}p} = -5 \mathrm{~V}\) y así el transistor está fuertemente encendido.

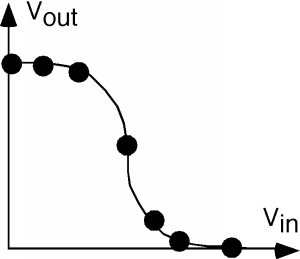

Tenemos una serie de diferentes “líneas de carga” en este caso, porque para cada una\(V_{\text{in}}\) tenemos una curva diferente tanto para los transistores de canal n como p. Esto se muestra en la Figura\(\PageIndex{8}\). Los puntos negros muestran el punto de intersección. Sigue algunas de las curvas a lo largo para ver si estás de acuerdo con dónde se han colocado los puntos. También hemos agregado un par de curvas punteadas para\(V_{\text{in}} = 2.5 \mathrm{~V}\) así poder obtener el punto de “vuelta”. Proyectar la ubicación de los puntos negros al eje\(V_{\text{ds-}n}\) (o\(V_{\text{out}}\)) nos dará un valor\(V_{\text{out}}\) para cada una de las tensiones de entrada,\(V_{\text{in}}\). La curva resultante se muestra en la Figura\(\PageIndex{9}\). Esto nos da una buena “sensación” de cómo funciona el inversor, y cómo varía la salida con la entrada. Tenga en cuenta que esta curva de transferencia es bastante simétrica alrededor de 2.5 voltios, y va desde +5 a 0 voltios en la salida.